|              | Cover Sheet and Revision Status |                    |                              |                     |  |  |

|--------------|---------------------------------|--------------------|------------------------------|---------------------|--|--|

| 版別<br>(Rev.) | DCC<br>No                       | 生效日<br>(Eff. Date) | 變更說明<br>(Change Description) | 發行人<br>(Originator) |  |  |

| 1.0          | 20230012                        | Jul.14 -2023       | New issue                    | Hank Lin            |  |  |

|              |                                 |                    |                              |                     |  |  |

|              |                                 |                    |                              |                     |  |  |

|              |                                 |                    |                              |                     |  |  |

|              |                                 |                    |                              |                     |  |  |

|              |                                 |                    |                              |                     |  |  |

|              |                                 |                    |                              |                     |  |  |

|              |                                 |                    |                              |                     |  |  |

|              |                                 |                    |                              |                     |  |  |

|              |                                 |                    |                              |                     |  |  |

|              |                                 |                    |                              |                     |  |  |

|              |                                 |                    |                              |                     |  |  |

|              |                                 |                    |                              |                     |  |  |

|              |                                 |                    |                              |                     |  |  |

|              |                                 |                    |                              |                     |  |  |

| General Description                                                                        | 1  |

|--------------------------------------------------------------------------------------------|----|

| Product Performance                                                                        | 1  |

| Features                                                                                   | 2  |

| Function Block Diagram         Figure 1: Function Block Diagram                            |    |

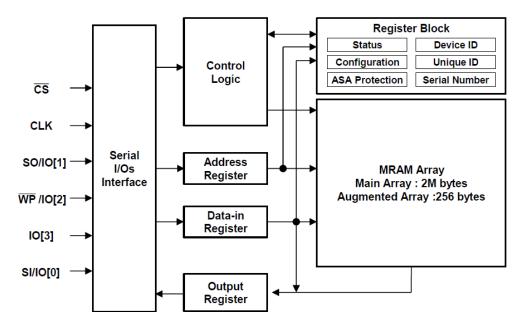

| Package Pin Configuration         Figure 2: Pinout                                         |    |

| Pin Descriptions                                                                           | 3  |

| Table 1: Pin Description                                                                   | 3  |

| Power On/Off Sequence: 1.8V Device                                                         |    |

| Figure 3 : Power-up/down Behavior : 1.8V Device                                            |    |

| Table 2: Power Up/Down Timing – 1.8V Device                                                |    |

| Power On/Off Sequence: 3.3V Device         Figure 3 : Power-up/down Behavior : 3.3V Device |    |

| Table 3 : Power Up/Down Timing – 3.3V Device                                               |    |

| Memory Organization                                                                        | 7  |

| Table 4: Memory Map                                                                        | 7  |

| Table 5 : Augmented 256-Byte Area Map                                                      | 7  |

| Table 6 : Register Address                                                                 | 8  |

| Instruction Command Set                                                                    |    |

| Table 7: Control Instruction Set                                                           | 8  |

| Table 8 : Read Register Instruction Set                                                    | 9  |

| Table 9 : Write Register Instruction Set                                                   | 9  |

| Table 10 : Read Memory Array Instruction Set                                               | 10 |

| Table 11 : Write Memory Array Instruction Set                                              | 10 |

| Table 12 : Augmented 256-Byte Area Instruction Set                                         | 11 |

| Register Description                                                                       | 11 |

| Table 13 : Status Register-Data Protection                                                 | 12 |

| Table 14 : Write Protection Modes                                                          | 12 |

| Table 15 : Block Protection Address Range Selection                             | 13 |

|---------------------------------------------------------------------------------|----|

| Table 16 : Augmented 256-Byte Area Protection Register – Read and Write         |    |

|                                                                                 |    |

| Table 17 : Configuration Register 1 – Read and Write                            |    |

| Table 18 : Configuration Register 2 – Read and Write                            | 15 |

| Table 19 : Read Latency Cycles vs. Maximum Frequency (Memory Area)              | 16 |

| Table 20 : Read Latency Cycles vs. Maximum Frequency (Augmented 256-Byte Area)  | 16 |

| Table 21 : Latency Cycles vs. Maximum Frequency (Read Any Register Instruction) | 16 |

| Table 22 : Configuration Register 3 – Read and Write                            | 16 |

| Table 23 : Configuration Register 4 – Read and Write                            | 17 |

| Table 24 : Device Identification Register – Read Only                           | 18 |

| Table 25 : Serial Number Register – Read and Write                              | 18 |

| Table 26 : Unique ID Register – Read Only                                       | 19 |

| Device Operation                                                                | 19 |

| General Operation                                                               | 19 |

| Figure 5 : SPI Clock Modes                                                      | 19 |

| SPI Interface Modes                                                             | 19 |

| Table 27 : Pin Assignment / Interface Modes                                     | 20 |

| Figure 6 : Location of MSB and LSB                                              | 16 |

| Figure 7 : MSB and LSB in DSPI and QSPI                                         | 16 |

| Figure 8 : Description of SDR Instruction Type                                  | 16 |

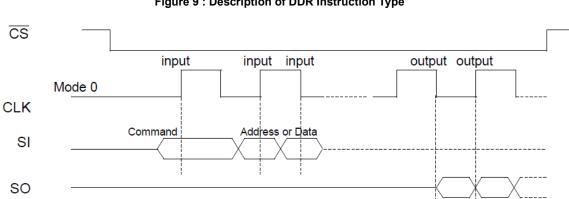

| Figure 9 : Description of DDR Instruction Type                                  | 16 |

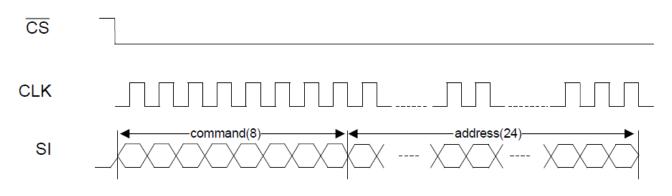

| Figure 10 : Description of command followed by Address (SSIP mode)              | 17 |

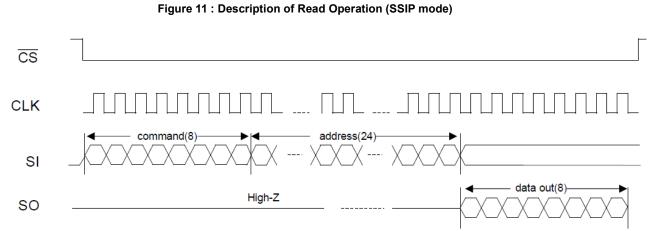

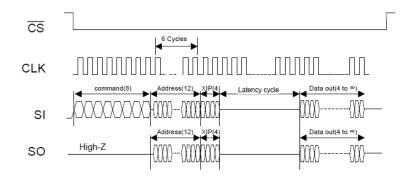

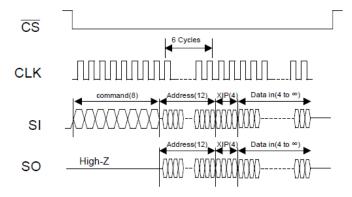

| Figure 11 : Description of Read Operation (SSIP mode)                           | 17 |

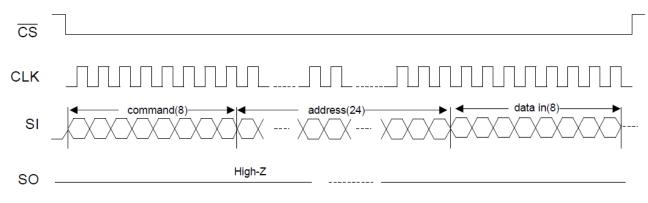

| Figure12 : Description of Write Operation (SSPI mode)                           | 18 |

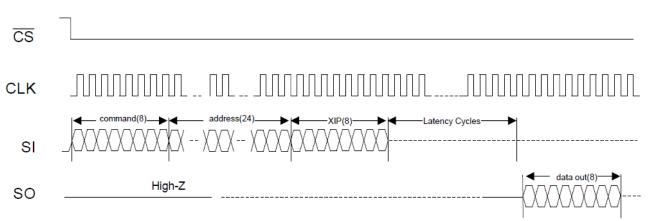

| Figure 13 : Description of Read Operation with XIP (SSIP mode)                  | 18 |

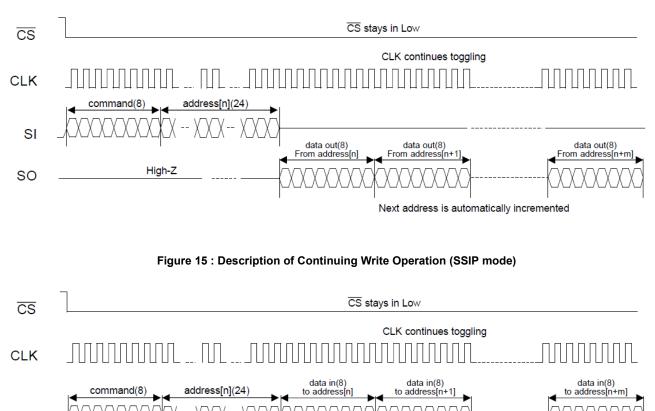

| Figure 14 : Description of Continuing Read Operation (SSIP mode)                | 19 |

| Figure 15 : Description of Continuing Write Operation (SSIP mode)               | 19 |

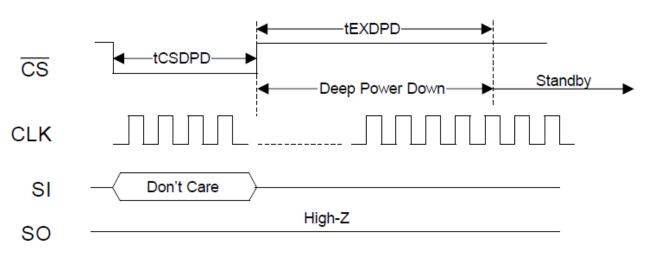

| Figure 16 : Entering Deep Power Down Mode (SSIP mode)                           | 20 |

| Figure 17 : Exit Deep Power Down Mode by CS                                     | 20 |

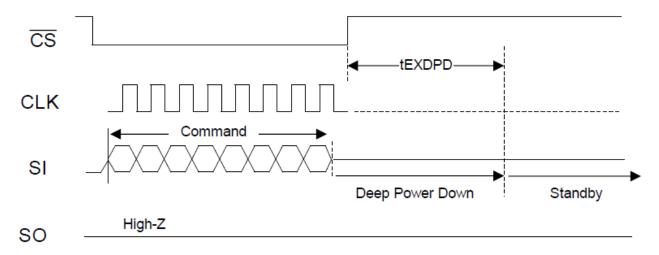

| Figure 18 : Exit Deep Power Down Mode by SPI Command                            | 21 |

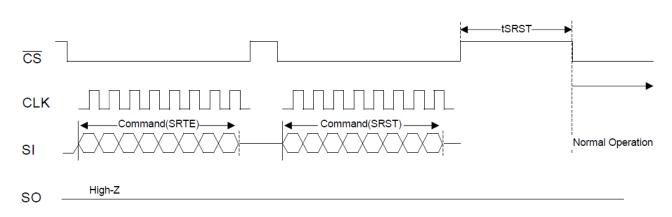

| Figure 19 : Software Reset Timing                                               | 21 |

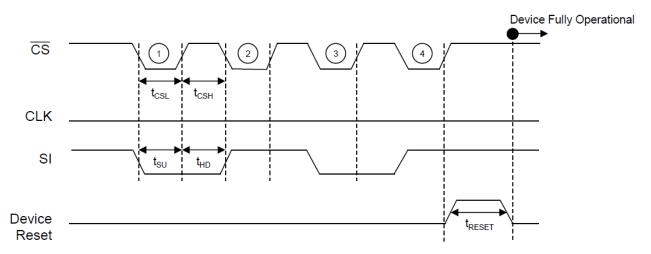

| Figure 20 : JEDEC Reset Operation Timing                                        | 22 |

| Table 28 : JEDEC Reset Operation & Timing : 1.8V Device                          | 22 |

|----------------------------------------------------------------------------------|----|

| Table29 : JEDEC Reset Operation & Timing : 3.3V Device                           | 22 |

| Electrical Specifications                                                        | 23 |

| Table 30 : Absolute Maximum Ratings                                              | 23 |

| Table 31 : Endurance, Retention and Magnetic Immunity                            | 23 |

| Table 32 : Recommended Operating Conditions                                      | 24 |

| Table 33 : Pin Capacitance                                                       |    |

| Table 34 : AC Test Conditions                                                    |    |

| Table 35 : DC Characteristics : 3.3V Device                                      |    |

| Table 36 : DC Characteristics : 1.8V Device                                      |    |

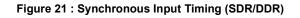

| Figure 21 : Synchronous Input Timing (SDR/DDR)                                   |    |

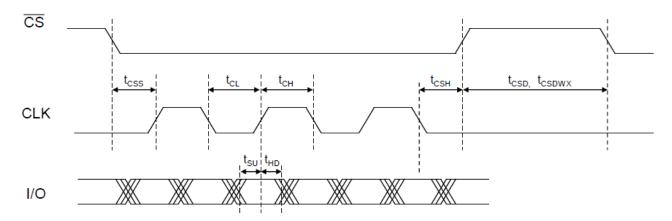

| Figure 22 : Synchronous Data Output Timing (SDR/DDR)                             |    |

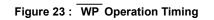

| Figure 23 : WP Operation Timing                                                  |    |

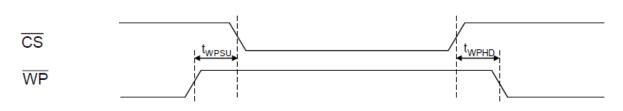

| Figure 24 : CS High Timing                                                       | 28 |

| Table 37 : CS High Time after Write Instruction : SDR=108MHz/DDR=54MHz           | 28 |

| Table 38 : CS High Time after Write Instruction : SDR=54MHz/DDR=27MHz            | 28 |

| Table 39 : CS High Time after Register/Augmented 256-Byte Area Write Instruction | 29 |

| Table 40 : AC Timing Parameter                                                   | 29 |

| Table 41 : Thermal Resistance                                                    |    |

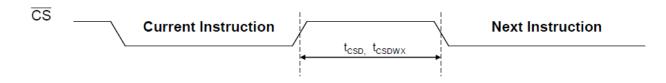

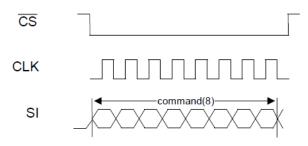

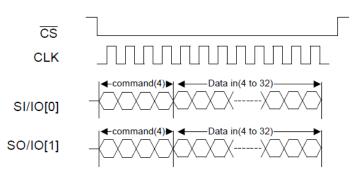

| Timing Description of Instruction Sets                                           |    |

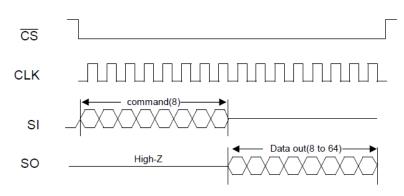

| Figure 25 : Timing Description of 1-0-0 Instruction Type                         |    |

|                                                                                  |    |

| Figure 26 : Timing Description of 1-0-1 Instruction Type (Read)                  |    |

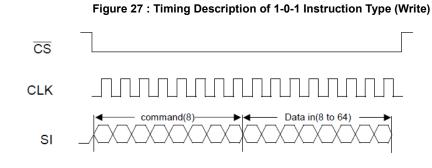

| Figure 27 : Timing Description of 1-0-1 Instruction Type (Write)                 |    |

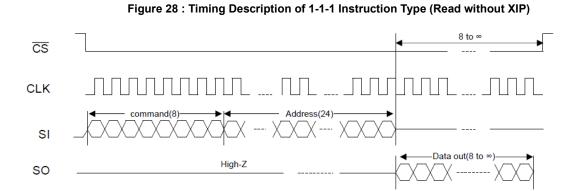

| Figure 28 : Timing Description of 1-1-1 Instruction Type (Read without XIP)      |    |

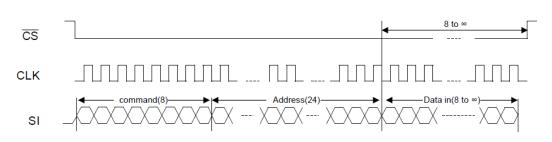

| Figure 29 : Timing Description of 1-1-1 Instruction Type (Write)                 |    |

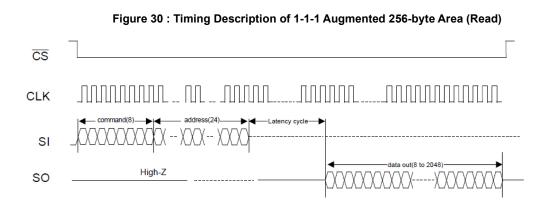

| Figure 30 : Timing Description of 1-1-1 Augmented 256-byte Area (Read)           |    |

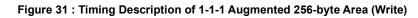

| Figure 31 : Timing Description of 1-1-1 Augmented 256-byte Area (Write)          | 32 |

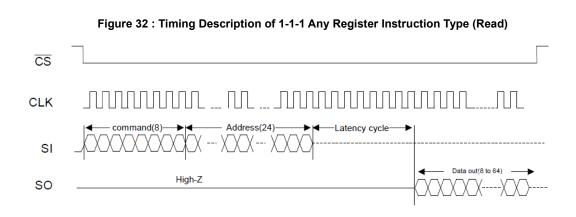

| Figure 32 : Timing Description of 1-1-1 Any Register Instruction Type (Read)  | 32 |

|-------------------------------------------------------------------------------|----|

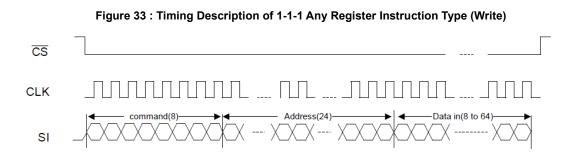

| Figure 33 : Timing Description of 1-1-1 Any Register Instruction Type (Write) | 33 |

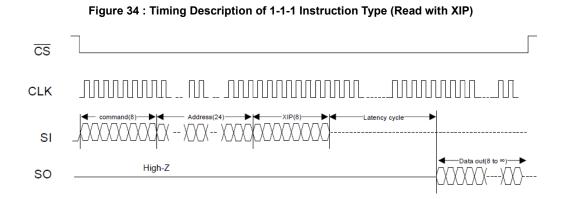

| Figure 34 : Timing Description of 1-1-1 Instruction Type (Read with XIP)      | 33 |

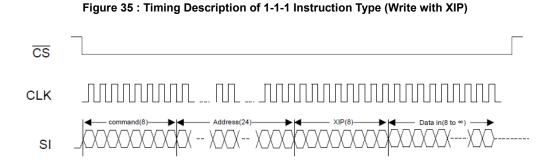

| Figure 35 : Timing Description of 1-1-1 Instruction Type (Write with XIP)     | 33 |

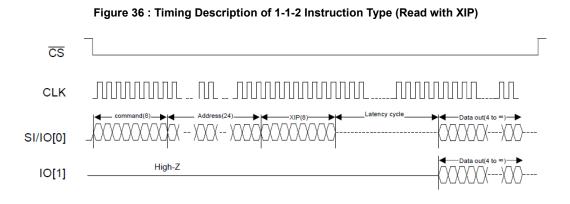

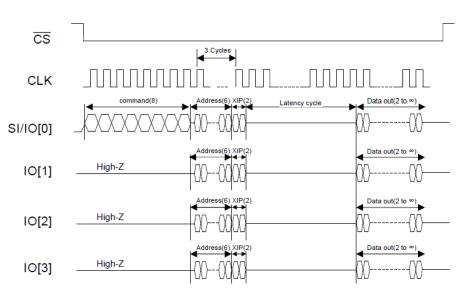

| Figure 36 : Timing Description of 1-1-2 Instruction Type (Read with XIP)      | 34 |

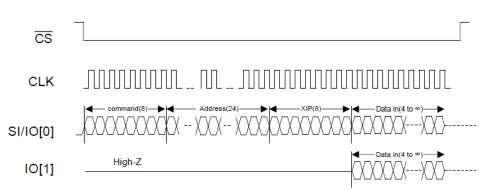

| Figure 37 : Timing Description of 1-1-2 Instruction Type (Write with XIP)     | 34 |

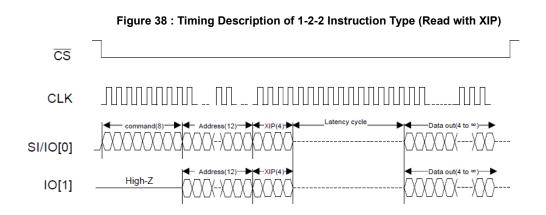

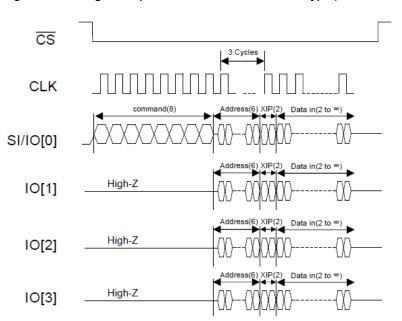

| Figure 38 : Timing Description of 1-2-2 Instruction Type (Read with XIP)      | 34 |

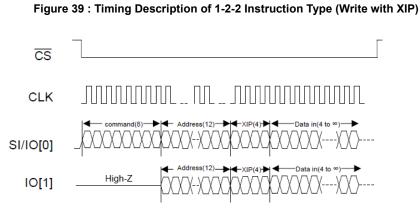

| Figure 39 : Timing Description of 1-2-2 Instruction Type (Write with XIP)     | 35 |

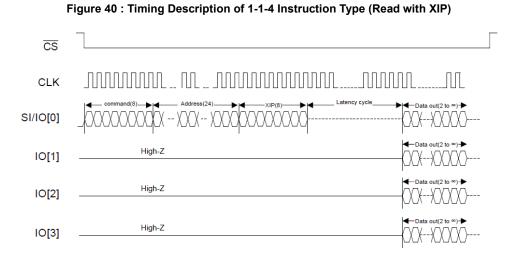

| Figure 40 : Timing Description of 1-1-4 Instruction Type (Read with XIP)      | 35 |

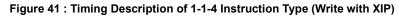

| Figure 41 : Timing Description of 1-1-4 Instruction Type (Write with XIP)     | 35 |

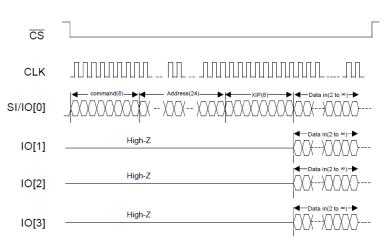

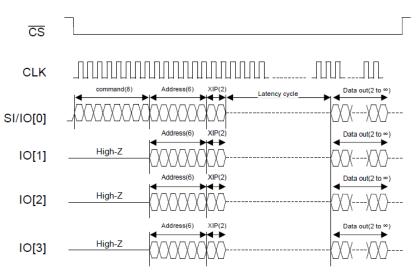

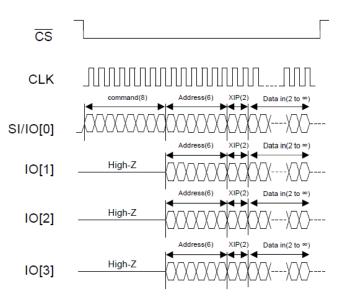

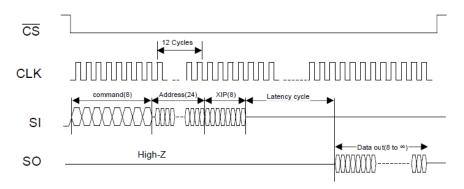

| Figure 42 : Timing Description of 1-4-4 Instruction Type (Read with XIP)      | 36 |

| Figure 43 : Timing Description of 1-4-4 Instruction Type (Write with XIP)     | 36 |

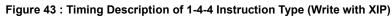

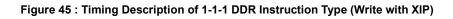

| Figure 44 : Timing Description of 1-1-1 DDR Instruction Type (Read with XIP)  | 37 |

| Figure 45 : Timing Description of 1-1-1 DDR Instruction Type (Write with XIP) | 37 |

| Figure 46 : Timing Description of 1-1-2 DDR Instruction Type (Read with XIP)  | 37 |

| Figure 47 : Timing Description of 1-1-2 DDR Instruction Type (Write with XIP) | 38 |

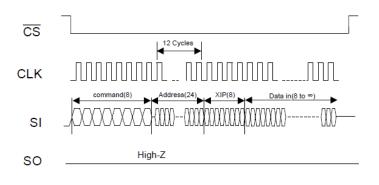

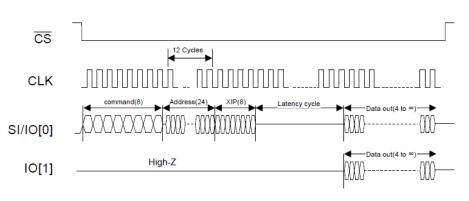

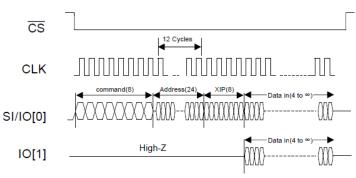

| Figure 48 : Timing Description of 1-2-2 DDR Instruction Type (Read with XIP)  | 38 |

| Figure 49 : Timing Description of 1-2-2 DDR Instruction Type (Write with XIP) | 38 |

| Figure 50 : Timing Description of 1-1-4 DDR Instruction Type (Read with XIP)  | 39 |

| Figure 51 : Timing Description of 1-1-4 DDR Instruction Type (Write with XIP) | 39 |

| Figure 52 : Timing Description of 1-4-4 DDR Instruction Type (Read with XIP)  | 40 |

| Figure 53 : Timing Description of 1-4-4 DDR Instruction Type (Write with XIP) | 40 |

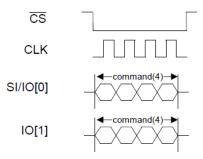

| Figure 54 : Timing Description of 2-0-0 Instruction Type                      | 41 |

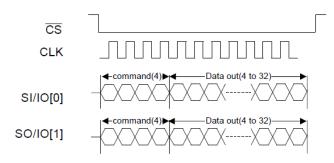

| Figure 55 : Timing Description of 2-0-2 Instruction Type (Read)               | 41 |

| Figure 56 : Timing Description of 2-0-2 Instruction Type (Write)              | 41 |

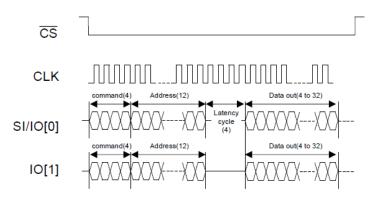

| Figure 57 : Timing Description of 2-2-2 Any Register Instruction Type (Read)  | 42 |

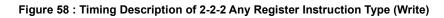

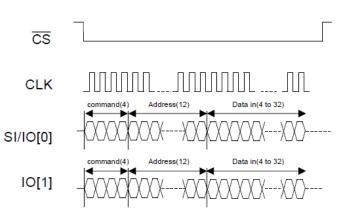

| Figure 58 : Timing Description of 2-2-2 Any Register Instruction Type (Write) | 42 |

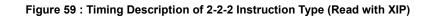

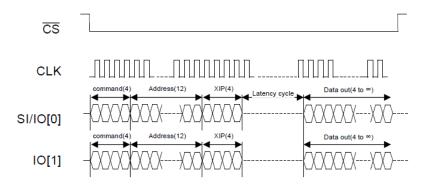

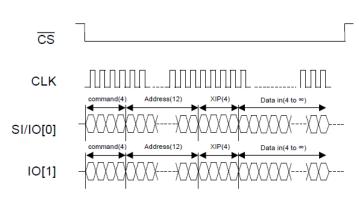

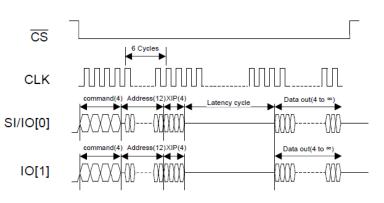

| Figure 59 : Timing Description of 2-2-2 Instruction Type (Read with XIP)      | 42 |

| Figure 60 : Timing Description of 2-2-2 Instruction Type (Write with XIP)     | 43 |

| Figure 61 : Timing Description of 2-2-2 DDR Instruction Type (Read with XIP)  | 43 |

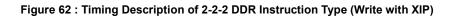

| Figure 62 : Timing Description of 2-2-2 DDR Instruction Type (Write with XIP) | 43 |

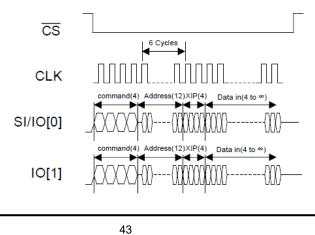

| Figure 63 : Timing Description of 4-0-0 Instruction Type                      | 44 |

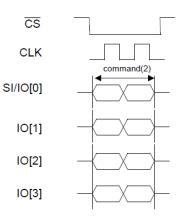

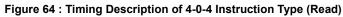

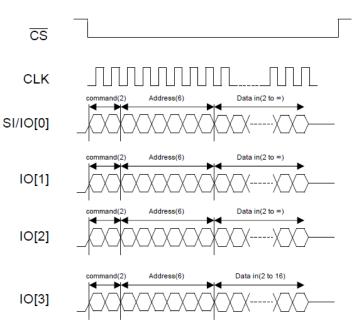

| Figure 64 : Timing Description of 4-0-4 Instruction Type (Read)               | 44 |

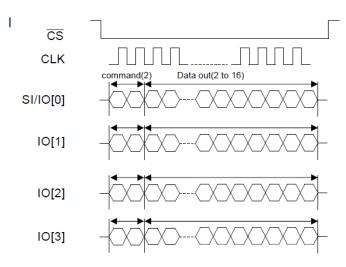

| Figure 65 : Timing Description of 4-0-4 Instruction Type (Write)              | 45 |

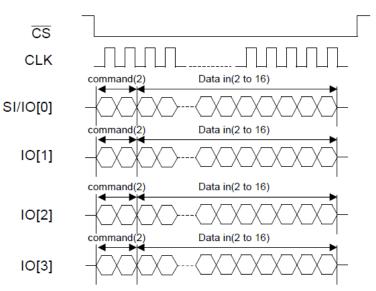

| Figure 66 : Timing Description of 4-4-4 Any Register Instruction Type (Read)  | 45 |

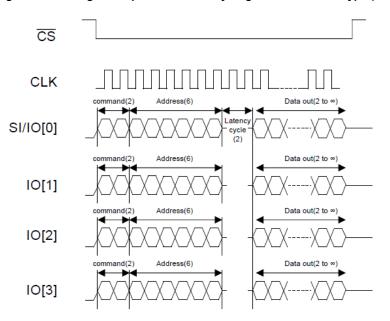

| Figure 67 : Timing Description of 4-4-4 Any Register Instruction Type (Write) | 46 |

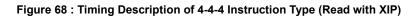

| Figure 68 : Timing Description of 4-4-4 Instruction Type (Read with XIP)      | 46 |

|                                                                               |    |

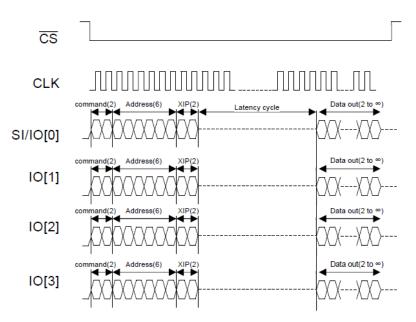

| Figure 69 : Timing Description of 4-4-4 Instruction Type (Write with XIP)     | 47 |

|-------------------------------------------------------------------------------|----|

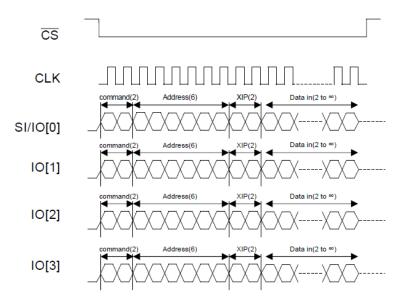

| Figure 70 : Timing Description of 4-4-4 DDR Instruction Type (Read with XIP)  | 47 |

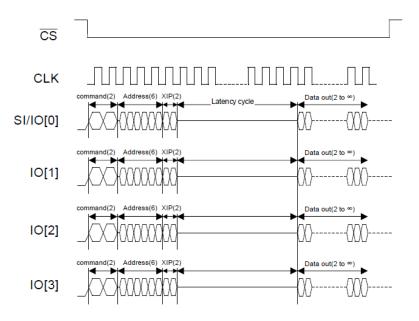

| Figure 71 : Timing Description of 4-4-4 DDR Instruction Type (Write with XIP) | 48 |

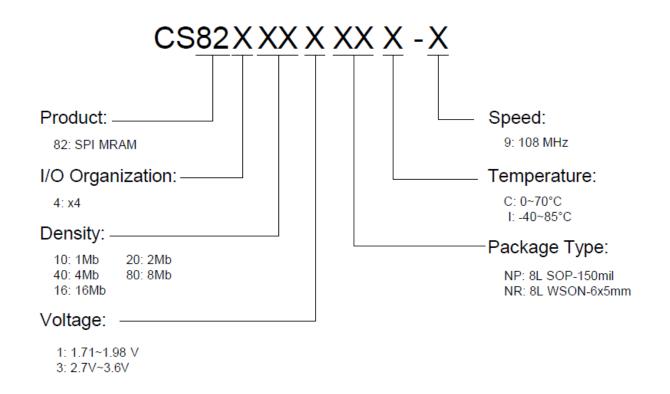

| Ordering Information                                                          | 48 |

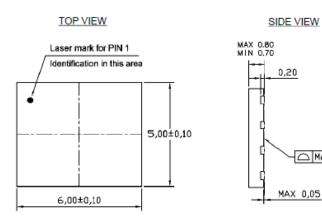

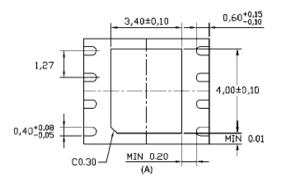

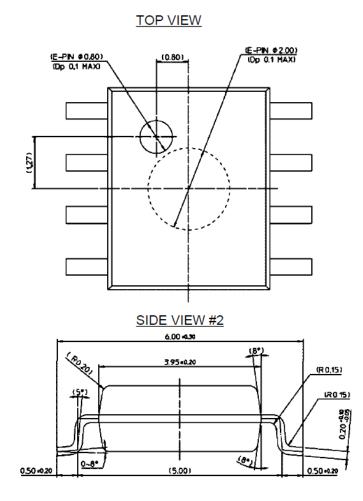

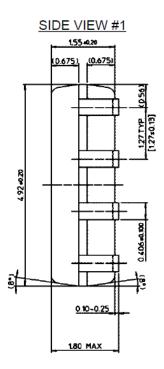

| Package Dimension                                                             |    |

| 8L WSON 6x5mm                                                                 | 49 |

| 8L SOP – 150mil                                                               | 50 |

|                                                                               |    |

### **General Description**

The device is a Spin-Transfer-Torque Magneto-resistive Random Access Memory (STT-MRAM). It features a SPI bus interface, XIP(execute-in-place) functionality, and hardware/software-based data protection mechanisms. SPI (Serial Peripheral Interface) is a synchronous serial communication interface with command, address and data signals.

It requires fewer pin counts than parallel interface and is easy to be configured on the system. The device is offered in density ranging from 1Mbit to 16Mbit. The device can replace Flash, FRAM or (nv)SRAM with same functionality and non-volatility.

The device provides various SPI modes to allow options for bandwidth expansion. SSPI (Single SPI) modes has single(1) pin for command signals. And user can select an option for how many pins to be allocated to address and data signals among 1 pin, 2 pins or 4 pins. DSPI (Dual SPI) modes provides dual(2) pins for command, address and data signals. QSPI (Quad SPI) modes provides Quad(4) pins for command, address and data signals.

The device has nonvolatile register bits – status register, configuration register, serial number register, augmented 256 bytes and protection register for augment bytes. These register bits are required to be set at least once on power-up after high temperature solder reflow process.

The device is available in small footprint 8-pad WSON and 8-pin SOIC packages. These packages are compatible with similar low-power volatile and non-volatile products.

### **Product Performance**

| Operation                                | Typical | Unito |       |

|------------------------------------------|---------|-------|-------|

| Operation                                | 1.8V    | 3.3V  | Units |

| Frequency(SDR)                           | 108 (   | MHz   |       |

| Frequency(DDR)                           | 54 (N   | MHz   |       |

| Standby Current                          | 280     | 330   | μA    |

| Deep Power Down Current                  | 25      | 80    | μA    |

| Active Read Current (4-4-4) SDR @108MHz  | 8       | 11    | mA    |

| Active Write Current (4-4-4) SDR @108MHz | 21      | 24    | mA    |

### **Features**

- Supports Serial Peripheral Interface with Mode 0 and Mode 3 - Single SPI (1-1-1, 1-1-2, 1-2-2, 1-1-4, 1-4-4) - Dual SPI (2-2-2) - Quad SPI (4-4-4)

- **Operating Frequency**

- Single Data Rates (SDR) : 108MHz -

- Double Data Rates (DDR) : 54MHz -

- Supports XIP for read and write operations

- Fast write time and single byte writable

- Data protection

- WP pin write protection -

- Block lock protection

- Nonvolatile status and configuration registers

- Identification

- 64-bit unique ID \_

- 64-bit serial number user writable

- Augmented 256-byte nonvolatile-area

- \_ 8L WSON (5.0mm x 6.0mm)

- 8L SOIC (150mil)

- Read and write with user-protection

- Deep power down for low power

- Supports JEDEC reset

- Memory cell : STT-MRAM

- Density 1Mb, 2Mb, 4Mb, 8Mb and 16Mb •

- Data Integrity : No external ECC required

- Data Endurance

- Unlimited read cycle

- 10<sup>14</sup> write cycles \_

- **Data Retention** •

- 10 years at 85°C

- Single Power Supply Operation

- **Operating Temperature Range**

- Commercial Temperature : 0°C to 70°C

- Industrial Temperature : -40°C to 85°C

- **RoHS** compliant packages

## 1Mb ~ 16Mb SPI MRAM

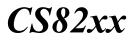

### **Function Block Diagram**

#### Figure 1: Function Block Diagram

### Package Pin Configuration

### **Pin Descriptions**

Table 1: Pin Description

| Pin       | Туре                    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

|-----------|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| CS        |                         | When CS is driven Low, read or write operation are initiated. When CS is driven High, the device enters standby mode, and all other input pins are ignored, and the output pins are tri-<br>stated. CS should be High at power-up to prevent abnormal write operation. This pin does not have internal pullup resistor.                                                                                                                                                                                                           |  |  |

| CLK       |                         | <ul> <li>In SDR(single data rate) mode, command, address and data inputs are latched on the rising edge of the clock. Data is output on the falling edge of the clock. In DDR(double data rate) mode command is latched on the rising edge of the clock and address and data inputs are latched on the rising and falling edges of the clock. Similarly, Data is output on both edges of the clock. The two SPI clock modes are supported as follows.</li> <li>SPI Mode 0 : SDR and DDR</li> <li>SPI Mode 3 : SDR only</li> </ul> |  |  |

| WP /IO[2] | Input<br>/Bidirectional | Write protects the status register in conjunction with the WREN bit (SR[1]) of the status register.<br>The writing of status register is protected in related with WP and WPEN. See "Table 14 : Write<br>Protection Modes". This pin does not have internal pullups, it cannot be left floating and must be<br>driven.<br>WP is valid in Single SPI and Dual SPI mode.<br>IO[2] : The bidirectional I/O in Quad SPI mode.                                                                                                         |  |  |

| IO[3]     | Bidirectional           | IO[3] : The bidirectional I/O in Quad SPI modes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| SI/IO[0]  | Input<br>/Bidirectional | SI : The serial input in Single SPI mode.<br>IO[0] : The bidirectional I/O in Dual and Quad SPI modes                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| SO/IO[1]  |                         | SO : The serial data output in Single SPI mode.<br>IO[1] : The bidirectional in Dual and Quad SPI modes.                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| Vcc       | Supply                  | Power pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| Vss       | Supply                  | Ground pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

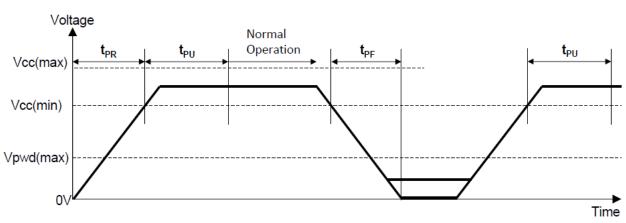

### Power On/Off Sequence: 1.8V Device

- When power-up, power-down or power-loss, CS must follow Vcc to provide data protection.

- It is recommended that CS must follow Vcc when Vcc is below Vcc(minimum) and during tPU.

- A 10KΩ pull-up resistor between Vcc and CS pin is recommended.

- Normal operation must start after tPU.

#### Figure 3 : Power-up/down Behavior : 1.8V Device

CS82xx

| Table 2: Power | Up/Down | Timina – 1 | 8V Device  |

|----------------|---------|------------|------------|

|                | Op/DOwn | runnig i   | .00 DCVICC |

| Parameter                                                       | Symbol               | Min  | Max  | Units |

|-----------------------------------------------------------------|----------------------|------|------|-------|

| Vcc Range                                                       | Vcc                  | 1.71 | 1.98 | V     |

| Vcc rising time                                                 | tPR <sup>(1)</sup>   | 30   | -    | μs/V  |

| Vcc falling time                                                | tPF <sup>(1)</sup>   | 30   | -    | μs/V  |

| Vcc(min) to CS Low (first instruction) time                     | tPU( <sup>1)</sup>   | 2.0  | -    | ms    |

| Vcc needed to below Vpwd for ensuring initialization will occur | VPWD <sup>(1)</sup>  | -    | 0.8  | V     |

| Software Reset Time                                             | tSRSE <sup>(1)</sup> | 2.0  | -    | ms    |

Notes:

1: These parameters are guaranteed by characterization; not tested in production.

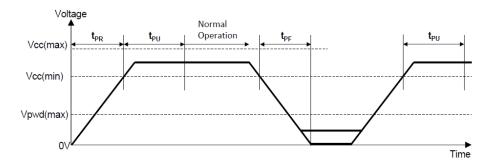

### Power On/Off Sequence: 3.3V Device

- When power-up, power-down or power-loss, CS must follow Vcc to provide data protection.

- It is recommended that CS must follow Vcc when Vcc is below Vcc (minimum) and during tPU.

- A 10K $\Omega$  pull-up resistor between Vcc and  $\overline{CS}$  pin is recommended.

- Normal operation must start after tPU.

#### Figure 3 : Power-up/down Behavior : 3.3V Device

CS82xx

Table 3 : Power Up/Down Timing – 3.3V Device

| Parameter                                                       | Symbol              | Min | Max | Units |

|-----------------------------------------------------------------|---------------------|-----|-----|-------|

| Vcc Range                                                       | Vcc                 | 2.7 | 3.6 | v     |

| Vcc rising time                                                 | tPR <sup>(1)</sup>  | 30  | -   | μs/V  |

| Vcc falling time                                                | tPF <sup>(1)</sup>  | 30  | -   | μs/V  |

| Vcc(min) to CS Low (first instruction) time                     | tPU <sup>(1)</sup>  | 2.0 | -   | ms    |

| Vcc needed to below Vpwd for ensuring initialization will occur | VPWD <sup>(1)</sup> | -   | 1.6 | V     |

Notes:

1: These parameters are guaranteed by characterization; not tested in production.

### **Memory Organization**

#### **Memory Map**

Table 4: Memory Map

| Density | Address Range     | 24-bit Ad           | dress [23:0]         |

|---------|-------------------|---------------------|----------------------|

| 1Mb     | 000000h – 01FFFFh | [23:17] – Logic '0' | [16:0] – Addressable |

| 2Mb     | 000000h – 03FFFFh | [23:18] – Logic '0' | [17:0] – Addressable |

| 4Mb     | 000000h – 07FFFFh | [23:19] – Logic '0' | [18:0] – Addressable |

| 8Mb     | 000000h – 0FFFFFh | [23:20] – Logic '0' | [19:0] – Addressable |

| 16Mb    | 000000h – 1FFFFFh | [23:21] – Logic '0' | [20:0] – Addressable |

#### Augmented 256-Byte Area Map

Table 5 : Augmented 256-Byte Area Map

| Density  | Address Range      | 24-bit Address [23:0] |                     |  |  |  |  |

|----------|--------------------|-----------------------|---------------------|--|--|--|--|

| 1Mb~16Mb | 000000h – 0000FFh1 | [23:8] – Logic '0'    | [7:0] - Addressable |  |  |  |  |

Notes:

### 1Mb ~ 16Mb SPI MRAM

1: The augmented 256-byte area is divided into 8 individually readable and writeable sections (32 bytes per section). After an individual section is written,

it can be written protected for each section to prevent further writing.

### **Register Address Map**

The device provides the register read/write instructions to read and write data of each register. In addition, the device provides the register read and/or write function based on addresses by RDAR(65h) and WRAR(71h) commands.

| Register Name                  | Address   |

|--------------------------------|-----------|

| Status Register                | 0x00000h  |

| Configuration Register 1       | 0x00002h  |

| Configuration Register 2       | 0x00003h  |

| Configuration Register 3       | 0x000004h |

| Configuration Register 4       | 0x00005h  |

| Device Identification Register | 0x000030h |

| Unique Identification Register | 0x000040h |

| Serial Number Register         | 0x000080h |

Table 6 : Register Address

Notes:

1: Register address space is different from the memory array and augmented 256-byte area.

### **Instruction Command Set**

| Instruction Name      | Command | Opcode | Interface Type      | XIP | Data | Data  | Latency | Max.      |

|-----------------------|---------|--------|---------------------|-----|------|-------|---------|-----------|

|                       |         | (Hex)  | (CMD-ADDR-Data)     |     | Rate | Bytes | Cycles  | Frequency |

| No operation          | NOOP    | 00     | 1-0-0, 2-0-0, 4-0-0 |     | SDR  |       |         | 108MHz    |

| Write Enable          | WREN    | 06     | 1-0-0, 2-0-0, 4-0-0 |     | SDR  |       |         | 108MHz    |

| Write Disable         | WRDI    | 04     | 1-0-0, 2-0-0, 4-0-0 |     | SDR  |       |         | 108MHz    |

| Enable DSPI           | DPIE    | 37     | 1-0-0, 4-0-0        |     | SDR  |       |         | 108MHz    |

| Enable QSPI           | QPIE    | 38     | 1-0-0, 2-0-0        |     | SDR  |       |         | 108MHz    |

| Enable SSPI           | SPIE    | FF     | 2-0-0, 4-0-0        |     | SDR  |       |         | 108MHz    |

| Enter Deep Power Down | DPDE    | B9     | 1-0-0, 2-0-0, 4-0-0 |     | SDR  |       |         | 108MHz    |

| Exit Deep Power Down  | DPDX    | AB     | 1-0-0, 2-0-0, 4-0-0 |     | SDR  |       |         | 108MHz    |

| Software Reset Enable | SRTE    | 66     | 1-0-0, 2-0-0, 4-0-0 |     | SDR  |       |         | 108MHz    |

| Software Reset*       | SRST    | 99     | 1-0-0, 2-0-0, 4-0-0 |     | SDR  |       |         | 108MHz    |

Table 7: Control Instruction Set

## 1Mb ~ 16Mb SPI MRAM

#### Notes:

1: Software Reset (SRST) requires Software Reset Enable (SRTE) implemented in advance.

2: SSPI mode is enabled after power-on, software reset or JEDEC reset.

| Table 8 : | Read | Register | Instruction Set |

|-----------|------|----------|-----------------|

|           |      |          |                 |

| Instruction Name                               | Command | Opcode |                     | XIP | Data<br>Poto | Data  | Latency |           |

|------------------------------------------------|---------|--------|---------------------|-----|--------------|-------|---------|-----------|

|                                                |         | (Hex)  | (CMD-ADDR-Data)     |     | Rate         | Bytes | Cycles  | Frequency |

| Read Status Register                           | RDSR    | 05     | 1-0-1, 2-0-2, 4-0-4 |     | SDR          | 1     |         | 108MHz    |

| Read Configuration Register 1                  | RDC1    | 35     | 1-0-1, 2-0-2, 4-0-4 |     | SDR          | 1     |         | 108MHz    |

| Read Configuration Register 2                  | RDC2    | 3F     | 1-0-1, 2-0-2, 4-0-4 |     | SDR          | 1     |         | 108MHz    |

| Read Configuration Register 3                  | RDC3    | 44     | 1-0-1, 2-0-2, 4-0-4 |     | SDR          | 1     |         | 108MHz    |

| Read Configuration Register 4                  | RDC4    | 45     | 1-0-1, 2-0-2, 4-0-4 |     | SDR          | 1     |         | 108MHz    |

| Read Configuration Register 1, 2, 3, 4         | RDCX    | 46     | 1-0-1, 2-0-2, 4-0-4 |     | SDR          | 4     |         | 108MHz    |

| Read Device ID                                 | RDID    | 9F     | 1-0-1, 2-0-2, 4-0-4 |     | SDR          | 4     |         | 108MHz    |

| Read Unique ID                                 | RUID    | 4C     | 1-0-1, 2-0-2, 4-0-4 |     | SDR          | 8     |         | 54MHz     |

| Read Serial Number Register                    | RDSN    | C3     | 1-0-1, 2-0-2, 4-0-4 |     | SDR          | 8     |         | 108MHz    |

| Read Augmented 256-byte<br>Protection Register | RDAP    | 14     | 1-0-1, 2-0-2, 4-0-4 |     | SDR          | 1     |         | 108MHz    |

| Read Any Register - Address<br>Based           | RDAR    | 65     | 1-1-1, 2-2-2, 4-4-4 |     | SDR          | 1,4,8 | 0       | 108MHz    |

Notes:

Registers do not wrap data during reads. Reading beyond the specified number of bytes will yield indeterminate data.

| Table  | 9: | Write | Reaister  | Instruction | Set |

|--------|----|-------|-----------|-------------|-----|

| i abio | ۰. |       | riegieter | moduom      | 000 |

| Instruction Name                 | Command | Opcode | Interface Type      | XIP | Data | Data  | Latency | Max.      |

|----------------------------------|---------|--------|---------------------|-----|------|-------|---------|-----------|

| Instruction Name                 | Command | (Hex)  | (CMD-ADDR-Data)     |     | Rate | Bytes | Cycles  | Frequency |

| Write Status Register            | WRSR    | 01     | 1-0-1, 2-0-2, 4-0-4 |     | SDR  | 1     |         | 108MHz    |

| Write Configuration Registers 1, | WRCX    | 87     | 1-0-1, 2-0-2, 4-0-4 |     | SDR  | 4     |         | 108MHz    |

| 2, 3, 4                          | WINGX   | 01     | 101,202,101         |     |      |       |         |           |

| Write Serial Number Register     | WRSN    | C2     | 1-0-1, 2-0-2, 4-0-4 |     | SDR  | 8     |         | 108MHz    |

| Write Augmented 256-byte         | WRAP    | 1A     | 1-0-1, 2-0-2, 4-0-4 |     | SDR  | 1     |         | 108MHz    |

| Protection Register              | WINAF   |        | 1-0-1, 2-0-2, 4-0-4 |     | SDR  | I     |         |           |

| Write Any Register - Address     | WRAR    | 71     | 1-1-1, 2-2-2, 4-4-4 |     | SDR  | 1,8   |         | 108MHz    |

| Based                            |         | / 1    | 1-1-1, 2-2-2, 4-4-4 |     | JUK  | 1,0   |         |           |

Notes:

## 1Mb ~ 16Mb SPI MRAM

1. Write Enable (WREN) should be implemented in advance of Write Register Instruction set regardless of CR4[1:0] setting.

2. The WREN prerequisite for write operation of memory array and augmented 256-byte area is described in Configuration Register 4.

| Instruction Name                    | Command | Opcode<br>(Hex) | Interface Type<br>(CMD-ADDR-<br>Data) | XIP |     |              | Latency<br>Cycles | Max.<br>Frequency |

|-------------------------------------|---------|-----------------|---------------------------------------|-----|-----|--------------|-------------------|-------------------|

| Read Memory Array - SDR             | READ    | 03              | 1-1-1                                 |     | SDR | 1→∞          |                   | 54MHz             |

| Fast Read Memory Array - SDR        | RDFT    | 0B              | 1-1-1, 2-2-2, 4-4-<br>4               | 0   | SDR | 1→∞          | 0                 | 108MHz            |

| Fast Read Memory Array - DDR        | DRFR    | 0D              | 1-1-1, 2-2-2, 4-4-<br>4               | 0   | DDR | 1→∞          | 0                 | 54MHz             |

| Read Dual Output Memory Array - SDR | RDDO    | 3B              | 1-1-2                                 | 0   | SDR | 1 <b>→</b> ∞ | 0                 | 108MHz            |

| Read Dual Output Memory Array - DDR | DRDO    | 3D              | 1-1-2                                 | 0   | DDR | 1→∞          | 0                 | 54MHz             |

| Read Quad Output Memory Array - SDR | RDQO    | 6B              | 1-1-4                                 | 0   | SDR | 1→∞          | 0                 | 108MHz            |

| Read Quad Output Memory Array – DDR | DRQO    | 6D              | 1-1-4                                 | 0   | DDR | 1→∞          | 0                 | 54MHz             |

| Read Dual I/O Memory Read - SDR     | RDDI    | BB              | 1-2-2                                 | 0   | SDR | 1→∞          | 0                 | 108MHz            |

| Read Dual I/O Memory Read - DDR     | DRDI    | BD              | 1-2-2                                 | 0   | DDR | 1→∞          | 0                 | 54MHz             |

| Read Quad I/O Memory Read - SDR     | RDQI    | EB              | 1-4-4                                 | 0   | SDR | 1→∞          | 0                 | 108MHz            |

| Read Quad I/O Memory Read - DDR     | DRQI    | ED              | 1-4-4                                 | 0   | DDR | 1→∞          | 0                 | 54MHz             |

Table 10 : Read Memory Array Instruction Set

Notes:

1: Read Instruction must include Latency cycles to meet operating frequency.

2: Latency is configurable through Configuration Register 2 (CR2[3:0]) and frequency dependent.

Required latency is described in Configuration Register 2.

| Instruction Name              | Command | Opcode<br>(Hex) | Interface Type<br>(CMD-ADDR-<br>Data) | XIP |     |     | Latency<br>Cycles | Max.<br>Frequency |

|-------------------------------|---------|-----------------|---------------------------------------|-----|-----|-----|-------------------|-------------------|

| Write Memory Array - SDR      | WRTE    | 02              | 1-1-1                                 |     | SDR | 1→∞ |                   | 108MHz            |

| Fast Write Memory Array - SDR | WRFT    | DA              | 1-1-1, 2-2-2, 4-4-4                   | 0   | SDR | 1→∞ |                   | 108MHz            |

| Fast Write Memory Array - DDR | DRFW    | DE              | 1-1-1, 2-2-2, 4-4-4                   | 0   | DDR | 1→∞ |                   | 54MHz             |

Table 11 : Write Memory Array Instruction Set

## 1Mb ~ 16Mb SPI MRAM

| Write Dual Input Memory Array-        | WDUI | A2 | 1-1-2 | 0 | SDR | 1→∞          | 108MHz |

|---------------------------------------|------|----|-------|---|-----|--------------|--------|

| SDR                                   |      |    |       |   |     |              |        |

| Write Dual Input Memory<br>Array– DDR | DWUI | A4 | 1-1-2 | 0 | DDR | 1 <b>→</b> ∞ | 54MHz  |

| Write Quad Input Memory Array- SDR    | WQDI | 32 | 1-1-4 | 0 | SDR | 1→∞          | 108MHz |

| Write Quad Input Memory Array- DDR    | DWQI | 31 | 1-1-4 | 0 | DDR | 1→∞          | 54MHz  |

| Write Dual I/O Memory Array - SDR     | WDIO | A1 | 1-2-2 | 0 | SDR | 1→∞          | 108MHz |

| Write Dual I/O Memory Array -DDR      | DWIO | A3 | 1-2-2 | ο | DDR | 1→∞          | 54MHz  |

| Write Quad I/O Memory Array - SDR     | WQIO | D2 | 1-4-4 | ο | SDR | 1→∞          | 108MHz |

| Write Quad I/O Memory Array - DDR     | DWQO | D1 | 1-4-4 | 0 | DDR | 1→∞          | 54MHz  |

Notes:

1: Write Enable (WREN) for array writing is configurable (Configuration Register 4 – CR4[1:0])

| Instruction Name                       | Command | Opcode<br>(Hex) | Interface Type<br>(CMD-ADDR-Data) | XIP | Data<br>Rate |           | Latency<br>Cycles | Max.<br>Frequency |

|----------------------------------------|---------|-----------------|-----------------------------------|-----|--------------|-----------|-------------------|-------------------|

| Read Augmented 256-Byte<br>Area - SDR  | RDAS    | 4B              | 1-1-1                             |     | SDR          | 1→<br>256 | 0                 | 108MHz            |

| Write Augmented 256-Byte<br>Area - SDR | WRAS    | 42              | 1-1-1                             |     | SDR          | 1→<br>256 |                   | 108MHz            |

Table 12 : Augmented 256-Byte Area Instruction Set

Notes:

1: The address bits ADDR[23:8] must be Logic '0' for this Instruction.

1: Write Enable (WREN) for array writing is configurable (Configuration Register 4 – CR4[1:0])

### **Register Description**

#### Status Register / Device Protection Register

The device offers both hardware and software-based data protection schemes. Hardware protection is through WP pin. Software protection is controlled by configuration bits in the Status register. Both schemes inhibit writing to the registers and memory array. Status Register contains options for enabling/disabling data protection. By controlling configuration bits in Status Register, use can protect data in memory array based on software protection schemes.

## 1Mb ~ 16Mb SPI MRAM

#### Table 13 : Status Register-Data Protection

| Bits  | Name  | Read/<br>Write | Default<br>State | Description                                                                                                                                             |

|-------|-------|----------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| SR[7] | WPEN  | R/W            | -                | Hardware Based WP Protect Bit<br>1: Protection Enabled – write protects when WP is Low<br>0: Protection Disabled – Doesn't write protect when WP is Low |

| SR[6] | SNPEN | R/W            | -                | Serial Number Protect Bit<br>1: Serial Number Write protected 0: Serial Number Writable                                                                 |

| SR[5] | ТВ    | R/W            | -                | Top/Bottom Memory Array Protect Selection<br>1: Bottom Protection Enabled (Lower Address Range) 0: Top Protection<br>Enabled (Higher Address Range)     |

| SR[4] | BP[2] | R/W            | -                |                                                                                                                                                         |

| SR[3] | BP[1] | R/W            | -                | Block Protection Bits                                                                                                                                   |

| SR[2] | BP[0] | R/W            | -                |                                                                                                                                                         |

| SR[1] | WREN  | R              | 0                | Write Protection Enable<br>1: Write Operation Protection Disabled<br>0: Write Operation Protection Enabled                                              |

| SR[0] | RSVD  | R              | -                | Reserved for future use                                                                                                                                 |

Note : SR[7:2] are nonvolatile bits.

#### Write Protection Modes

WPEN bit  $(SR_{[7]})$  is used in conjunction with the WREN bit  $(SR_{[1]})$  and the WP pin to provide hardware block protection. SR\_{[7:2]} will remain set from the nonvolatile registers whenever the power is on. The WREN bit is volatile and set "1" by the Write Enable command. It is set to "0" at power up. The device enters hardware protection when the WP input is low and the Status Register WPEN bit is set to 1, and the status and configuration register bits cannot be changed. The device exits from hardware protection when the /WP pin goes high or WPEN bit is set to 0, and the register bits can be changed.

| WREN | WPEN | WP (Pin) |             | Memory <sup>1</sup> Array<br>Protected Area | Memory <sup>1</sup> Array<br>Unprotected Area |  |  |

|------|------|----------|-------------|---------------------------------------------|-----------------------------------------------|--|--|

| 0    | х    | Х        | Protected   | Protected                                   | Protected                                     |  |  |

| 1    | 0    | Х        | Unprotected | Protected                                   | Unprotected                                   |  |  |

| 1    | 1    | 0        | Protected   | Protected                                   | Unprotected                                   |  |  |

| 1    | 1    | 1        | Unprotected | Protected                                   | Unprotected                                   |  |  |

Table 14 : Write Protection Modes

Notes:

1: Memory address range protection based on Block Protection Bits

2. X: Don't Care – Can be Logic '0' or '1'

3. Protected: Write protected, Unprotected: Writable

#### **Block Protection Modes**

The write protection blocks for the memory array are determined by the status register bits (TB and BP[2:0]) as Table 15. TB and BP[2:0] can be modified by WRSR command when the  $\overline{WP}$  input is high or the Status Register WPEN bit is set to 0, and MAPLK(CR1[2]) is set to 0.

CS82xx

| ТВ  | BP[2] | BP[1] | BP[0] | Protected<br>Portion | 1Mb       | 2Mb       | 4Mb       | 8Mb       | 16Mb      |

|-----|-------|-------|-------|----------------------|-----------|-----------|-----------|-----------|-----------|

| 0/1 | 0     | 0     | 0     | None                 | None      | None      | None      | None      | None      |

|     |       | _     |       | 1/04                 | 01F800h – | 03F000h – | 07E000h – | 0FC000h – | 1F8000h – |

| 0   | 0     | 0     | 1     | Upper 1/64           | 01FFFFh   | 03FFFFh   | 07FFFFh   | 0FFFFFh   | 1FFFFFh   |

|     | 0     | 4     | 0     | Ling og 1/00         | 01F000h – | 03E000h – | 07C000h – | 0F8000h – | 1F0000h – |

| 0   | 0     | 1     | 0     | Upper 1/32           | 01FFFFh   | 03FFFFh   | 07FFFFh   | 0FFFFFh   | 1FFFFFh   |

|     | 0     | 1     | 1     | Linner 1/16          | 01E000h – | 03C000h - | 078000h – | 0F0000h – | 1E0000h – |

| 0   | 0     | I     | I     | Upper 1/16           | 01FFFFh   | 03FFFFh   | 07FFFFh   | 0FFFFFh   | 1FFFFFh   |

| 0   | 1     | 0     | 0     | Upper 1/8            | 01C000h - | 038000h – | 070000h – | 0E0000h – | 1C0000h – |

| 0   | I     | 0     | 0     | Opper 1/6            | 01FFFFh   | 03FFFFh   | 07FFFFh   | 0FFFFFh   | 1FFFFFh   |

| 0   | 1     | 0     | 1     | Upper 1/4            | 018000h – | 030000h – | 060000h – | 0C0000h   | 180000h – |

| 0   | I     | 0     | I     | Opper 1/4            | 01FFFFh   | 03FFFFh   | 07FFFFh   | 0FFFFFh   | 1FFFFFh   |

| 0   | 1     | 1     | 0     | Upper 1/2            | 010000h – | 020000h – | 040000h – | 080000h – | 100000h – |

| 0   | 1     |       | 0     |                      | 01FFFFh   | 03FFFFh   | 07FFFFh   | 0FFFFFh   | 1FFFFFh   |

| 1   | 0     | 0     | 1     | Lower 1/64           | 000000h – |

|     | 0     | 0     | I     | Lowel 1/04           | 0007FFh   | 000FFFh   | 001FFFh   | 003FFFh   | 007FFFh   |

| 1   | 0     | 1     | 0     | Lower 1/32           | 000000h – |

|     | 0     | I     | 0     | LOWEI 1/32           | 000FFFh   | 001FFFh   | 003FFFh   | 007FFFh   | 00FFFFh   |

| 1   | 0     | 1     | 1     | Lower 1/16           | 000000h – |

|     | 0     |       | -     | Lower 1/10           | 001FFFh   | 003FFFh   | 007FFFh   | 00FFFFh   | 01FFFFh   |

| 1   | 1     | 0     | 0     | Lower 1/8            | 000000h – |

|     | I     | 0     | 0     | LOWEI 1/8            | 003FFFh   | 007FFFh   | 00FFFFh   | 01FFFFh   | 03FFFFh   |

| 1   | 1     | 0     | 1     | Lower 1/4            | 000000h – |

|     |       | 0     |       |                      | 007FFFh   | 00FFFFh   | 01FFFFh   | 03FFFFh   | 07FFFFh   |

| 1   | 1     | 1     | 0     | Lower 1/2            | 000000h – |

Table 15 : Block Protection Address Range Selection

## 1Mb ~ 16Mb SPI MRAM

|     |   |   |   |     | 00FFFFh   | 01FFFFh   | 03FFFFh   | 07FFFFh   | 0FFFFFh   |

|-----|---|---|---|-----|-----------|-----------|-----------|-----------|-----------|

| 0/1 | 1 | 1 | 1 | All | 000000h – |

| 0/1 |   |   |   | All | 01FFFFh   | 03FFFFh   | 07FFFFh   | 0FFFFFh   | 1FFFFFh   |

#### Augmented 256-Byte Area Protection

Augmented 256-Byte Area Protection register contains options for enabling/disabling data protection for eight 32-byte sections.

| Bits   | Name    | Address Range     | Read/ | Default | Description            |

|--------|---------|-------------------|-------|---------|------------------------|

| Dits   | Name    | Address Range     | Write | State   | Description            |

| ASP[7] | ASPS[7] | 0000E0h – 0000FFh | R/W   | 0       |                        |

| ASP[6] | ASPS[6] | 0000C0h – 0000DFh | R/W   | 0       |                        |

| ASP[5] | ASPS[5] | 0000A0h – 0000BFh | R/W   | 0       |                        |

| ASP[4] | ASPS[4] | 000080h – 00009Fh | R/W   | 0       | 1: Protection Enabled  |

| ASP[3] | ASPS[3] | 000060h – 00007Fh | R/W   | 0       | 0: Protection Disabled |

| ASP[2] | ASPS[2] | 000040h – 00005Fh | R/W   | 0       |                        |

| ASP[1] | ASPS[1] | 000020h – 00003Fh | R/W   | 0       |                        |

| ASP[0] | ASPS[0] | 000000h – 00001Fh | R/W   | 0       |                        |

Table 16 : Augmented 256-Byte Area Protection Register - Read and Write

Note : ASP[7:0] are nonvolatile bits.

### **Configuration Register 1 (Read/Write)**

Configuration Register 1 controls locking/unlocking data protection options set in the Status register.

Once locked, the protection options cannot be changed in the Status register.

| Bits   | Name  | Read/<br>Write | Default<br>State | Selection Options                                                                      |

|--------|-------|----------------|------------------|----------------------------------------------------------------------------------------|

| CR1[7] | RSVD  | R/W            | -                | Reserved for future use                                                                |

| CR1[6] | RSVD  | R/W            | -                | Reserved for future use                                                                |

| CR1[5] | RSVD  | R/W            | -                | Reserved for future use                                                                |

| CR1[4] | RSVD  | R/W            | -                | Reserved for future use                                                                |

| CR1[3] | RSVD  | R/W            | -                | Reserved for future use                                                                |

| CR1[2] | MAPLK | R/W            | -                | Status Register TB, BP[2:0] Protect 1: Lock TB and BP[2:0]<br>0: Unlock TB and BP[2:0] |

Table 17 : Configuration Register 1 - Read and Write

## 1Mb ~ 16Mb SPI MRAM

| CR1[1] | RSVD  | R/W     | - | Reserved for future use                                                                                       |

|--------|-------|---------|---|---------------------------------------------------------------------------------------------------------------|

| CR1[0] | ASPLK | K R/W - |   | Augmented 256-Byte Area Data Protection<br>1: Write Protection for Augmented Area Data regardless of ASP[7:0] |

|        |       |         |   | 0: Write Protection for Augmented Area Data depending on ASP[7:0]                                             |

Note : CR1[7:0] are nonvolatile bits.

### Configuration Register 2 (Read/Write)

Configuration Register 2 controls the interface type along with memory array access latency.

| Bits   | Name  | Read/ | Default | Description                                                         |

|--------|-------|-------|---------|---------------------------------------------------------------------|

| DIIS   | Name  | Write | State   | Description                                                         |

| CR2[7] | RSVD  | R/W   | -       | Reserved for future use                                             |

|        |       | Р     | 0       | Quad SPI (QPI 4-4-4) Interface Mode 1: Quad SPI (QPI 4-4-4) Enabled |

| CR2[6] | QPIEN | R     | 0       | 0: Single SPI (SPI 1-X-X) Enabled                                   |

| CR2[5] | RSVD  | R/W   | -       | Reserved for future use                                             |

| 0.7.0  | DPIEN | в     | 0       | Dual SPI (DPI 2-2-2) Interface Mode 1: Dual SPI (DPI 2-2-2) Enabled |

| CR2[4] | DPIEN | R     | 0       | 0: Single SPI (SPI 1-X-X) Enabled                                   |

|        |       |       |         | Read Latency Selection Bits : CR2[3:0]                              |

|        |       |       |         | 0000: 0 Cycle                                                       |

| CR2[3] | RL[3] |       | -       | 0001: 1 Cycle                                                       |

|        |       |       |         | 0010: 2 Cycles                                                      |

|        |       |       |         | 0011: 3 Cycles                                                      |

|        |       |       |         | 0100: 4 Cycles                                                      |

| CR2[2] | RL[2] |       | -       | 0101: 5 Cycles                                                      |

|        |       |       |         | 0110: 6 Cycles                                                      |

|        |       | R/W   |         | 0111: 7 Cycles                                                      |

|        |       |       |         | 1000: 8 Cycles                                                      |

| CR2[1] | RL[1] |       | -       | 1001: 9 Cycles                                                      |

|        |       |       |         | 1010: 10 Cycles                                                     |

|        |       |       |         | 1011: 11 Cycles                                                     |

|        |       |       |         | 1100: 12 Cycles                                                     |

| CR2[0] | RL[0] |       | -       | 1101: 13 Cycles                                                     |

|        |       |       |         | 1110: 14 Cycles                                                     |

|        |       |       |         | 1111: 15 Cycles                                                     |

Table 18 : Configuration Register 2 - Read and Write

Notes:

### 1Mb ~ 16Mb SPI MRAM

#### 1. Read Latency is frequency dependent.

2. Read(03h) does not depend on Read latency Selection Bits, CR2[3:0].

3. CR2[7,5,3:0] are nonvolatile bits.

| Read Type                                       | Data Rate | XIP | Latency Cycles | Max Frequency |

|-------------------------------------------------|-----------|-----|----------------|---------------|

| 1-1-1 (READ 03h)                                | SDR       | -   | 0              | 54MHz         |

| 1-1-1, 1-1-2, 1-2-2, 2-2-2, 1-1-4, 1-4-4, 4-4-4 | SDR       | 0   | 6.45           | 108MHz        |

| 1-1-1, 1-1-2, 1-2-2, 2-2-2, 1-1-4, 1-4-4, 4-4-4 | DDR       | 0   | 6-15           | 54MHz         |

#### Table 19 : Read Latency Cycles vs. Maximum Frequency (Memory Area)

Notes:

Read(03h) does not depend on Read latency Selection Bits, CR2[3:0]. The latency of Read(03h) is always 0-cycle

#### Table 20 : Read Latency Cycles vs. Maximum Frequency (Augmented 256-Byte Area)

| Read Type        | Data Rate | XIP | Latency Cycles | Max Frequency |

|------------------|-----------|-----|----------------|---------------|

| 1-1-1 (RDAS 4Bh) | SDR       | -   | 6-15           | 54MHz         |

| 1-1-1 (RDAS 4Bh) | SDR       | -   | 8-15           | 108MHz        |

#### Table 21 : Latency Cycles vs. Maximum Frequency (Read Any Register Instruction)

| Read Type        | Data Rate | XIP | Latency Cycles | Max Frequency |

|------------------|-----------|-----|----------------|---------------|

| 1-1-1 (RDAR 65h) | SDR       | -   | 8              | 108MHz        |

| 2-2-2 (RDAR 65h) | SDR       | -   | 4              | 108MHz        |

| 4-4-4 (RDAR 65h) | SDR       | -   | 2              | 108MHz        |

Notes:

1. RDAR(65h, read any register instruction) does not depend on Read latency Selection Bits, CR2[3:0].

CS82xx

### **Configuration Register 3 (Read/Write)**

Configuration Register 3 controls the output driver strength along with the boundary size of read data wrapping.

| Bits   | Name    | Read/ Write | Description                                                                                     |  |  |

|--------|---------|-------------|-------------------------------------------------------------------------------------------------|--|--|

| CR3[7] | DRV[2]  |             | Output Driver Strength Selection DRV[2:0]<br>3.3V 1.8V<br>000: 36Ω 35Ω                          |  |  |

| CR3[6] | DRV[1]  | R/W         | 001: 100Ω 95Ω<br>010: 75Ω 63Ω<br>011: 60Ω 50Ω<br>100: 48Ω 40Ω                                   |  |  |

| CR3[5] | DRV[0]  |             | 101: 41Ω 30Ω<br>110: 29Ω 26Ω<br>111: 24Ω 22Ω                                                    |  |  |

| CR3[4] | WRPEN   | R/W         | Read WRAP Enable 1: Read Wrap Enabled<br>0: Read Wrap Disabled                                  |  |  |

| CR3[3] | RSVD    | R/W         | Reserved for future use                                                                         |  |  |

| CR3[2] | WRPL[2] |             | Wrap length configuration WRPL[2:0] 000: 16-byte wrap<br>001: 32-byte wrap<br>010: 64-byte wrap |  |  |

| CR3[1] | WRPL[1] | R/W         | 011: 128-byte wrap<br>100: 256-byte wrap                                                        |  |  |

| CR3[0] | WRPL[0] |             | 101: 512-byte wrap<br>110: 1K-byte wrap<br>111: Reserved                                        |  |  |

Table 22 : Configuration Register 3 - Read and Write

Notes:

Default output strength is DRV[2:0]=000.

CR3[7:0] are nonvolatile bits.

## 1Mb ~ 16Mb SPI MRAM

|                                                                                               | Description                                                                                               |  |  |

|-----------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|--|--|

|                                                                                               | Read and write operation : continuous mode                                                                |  |  |

| WRPEN(CR3[4])<br>=Low                                                                         | Read or write operation starts at the input address, and once the address reaches the maximum address     |  |  |

|                                                                                               | boundary, it automatically returns to minimum address(000000h) until CS goes to high.                     |  |  |

|                                                                                               | Read operations : wrap mode                                                                               |  |  |

|                                                                                               | Read wrap mode is enabled when WRPEN(CR3[4]) is High, and the read data wrap length is controlled by      |  |  |

|                                                                                               | WRPL[2:0]. The output data starts at the input address, data are output sequentially. Once it reaches the |  |  |

|                                                                                               | ending boundary, the output will wrap around to the beginning boundary automatically until CS is pulled   |  |  |

| WRPEN(CR3[4])                                                                                 | high.                                                                                                     |  |  |

| =High                                                                                         |                                                                                                           |  |  |

|                                                                                               | Write operation : continuous mode                                                                         |  |  |

| Write operation starts at the input address, and once the address reaches the maximum address |                                                                                                           |  |  |

|                                                                                               | it automatically returns to minimum address(000000h) until CS goes to high.                               |  |  |

### **Configuration Register 4 (Read/Write)**

Configuration Register 4 controls Write Enable protection (WREN – Status Register) reset functionality during memory array writing1. This functionality makes SPI MRAM compatible to other SPI devices.

| Bits     | Name     | Read/<br>Write | Default<br>State | Selection Options                                                                                                                                                                                                                                                                          |

|----------|----------|----------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CR4[7:2] | RSVD     |                | -                | Reserved for future use                                                                                                                                                                                                                                                                    |

| CR4[1]   | WRENS[1] | R/W            | -                | <ul> <li>00: Normal: WREN is prerequisite to all Memory Array and Augmented 256-byte Area Write instruction. (WREN is reset after CS goes High)</li> <li>01: SRAM: WREN is not a prerequisite to Memory Array and Augmented 256-byte Area Write instruction (WREN is ignored)</li> </ul>   |

| CR4[0]   | WRENS[0] |                | -                | <ul> <li>10: Back-to-Back: WREN is prerequisite to only the first Memory Array</li> <li>Write or Augmented 256-byte Area instruction. WREN disable instruction</li> <li>must be executed to reset WREN. (WREN does not reset after CS goes</li> <li>High)</li> <li>11: Reserved</li> </ul> |

#### Table 23 : Configuration Register 4 - Read and Write

Notes:

1. Write Enable protection (WREN – Status Register) for Registers is maintained irrespective of the Configuration Register 4 settings. In other words, all register write Instructions require WREN to be set and WREN resets once  $\overline{CS}$  goes High for the write instruction. CR4[1:0] only affects the writing for

memory and augmented 256-bytes area.

2. CR4[7:0] are nonvolatile bits.

### **Device Identification Register (Read Only)**

Device identification register contains Manufacturing ID along with device configuration information.

|   | Bits     | Manufacturer ID | Device Configuration |           |             |          |         |

|---|----------|-----------------|----------------------|-----------|-------------|----------|---------|

| Γ |          |                 | Interface            | Voltage   | Temperature | Density  | Freq    |

|   | ID[31:0] | ID[31:24]       | ID[23:20]            | ID[19:16] | ID[15:12]   | ID[11:8] | ID[7:0] |

| Table 24 : De | evice Identifi | ration Regis | ter – Read  | Only |

|---------------|----------------|--------------|-------------|------|

| 1 4010 24.00  |                | Jalion Negis | iei – iteau | Only |

CS82xx

| Manufacturer ID | Interface   | Voltage                    | Temperature       | Density     | Frequency         |

|-----------------|-------------|----------------------------|-------------------|-------------|-------------------|

| 31-24           | 23-20       | 19-16                      | 15-12             | 11-8        | 7-0               |

|                 |             |                            |                   | 0001 : 1Mb  |                   |

|                 | 0000 : QSPI | 0001 : 3.3V<br>0010 : 1.8V |                   | 0010 : 2Mb  |                   |

| 1101 1001       |             |                            | 0000 : -40ºC~85⁰C | 0011 : 4Mb  | 00000001 : 108MHz |

|                 |             |                            |                   | 0100 : 8Mb  |                   |

|                 |             |                            |                   | 0101 : 16Mb |                   |

### Serial Number Register (Read/Write)

The device provides 64-bits Serial Number register and the user can write it.

#### Table 25 : Serial Number Register - Read and Write

| Bits     | Name | Description         | Read/ Write | State         |

|----------|------|---------------------|-------------|---------------|

| SN[63:0] | SN   | Serial Number Value | R/W         | User writable |

Notes:

1: Serial Number Bits are non-volatile, and user should write the data after solder reflow process.

### **Unique Identification Register (Read Only)**

Unique Identification register contains a number unique to every device.

### 1Mb ~ 16Mb SPI MRAM

| Bits      | Name | Description           | Read/ Write | Selection Options                                    |

|-----------|------|-----------------------|-------------|------------------------------------------------------|

|           | UID  | Unique Identification | R           | Value stored is written in the factory and is device |

| UID[63:0] | UD   | Number Value          |             | specific                                             |

### **Device Operation**

### **General Operation**

Before an instruction is issued, status register should be checked to ensure device is ready for the intended operation. When correct command is input to this device, it enters active mode and remains in active mode until next  $\overline{CS}$  rising edge. Do not enter an invalid opcode(except instruction set). When  $\overline{CS}$  goes to high, the device enters standby mode. All communication between a host and the device is in the form of commands. commands define the operation that must be executed. Instruction consists of a command followed by an optional address modifier and data transferred. All command, address and data information are transferred sequentially.

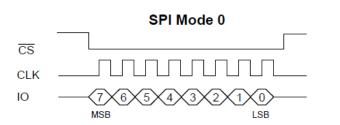

#### **SPI Clock Modes**

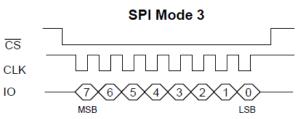

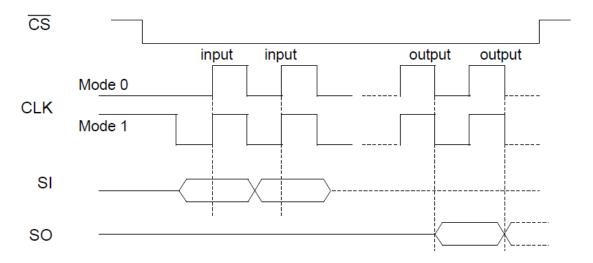

- The following two SPI clock modes are supported.

- SPI Mode 0 (CPOL = 0, CPHA = 0) SDR and DDR

- SPI Mode 3 (CPOL = 1, CPHA = 1) SDR only

#### Figure 5 : SPI Clock Modes

Clock stays in low level during idle state and starts toggling by going high

### SPI Interface Modes

Clock stays in high level during idle state and starts toggling by going low

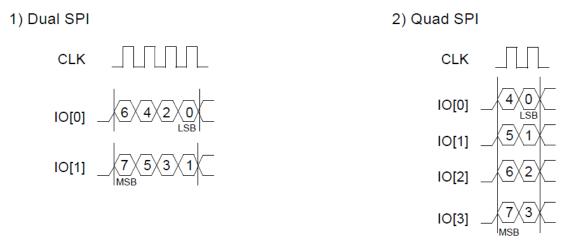

• The device supports 3 categories of SPI interface modes.

- Single SPI (SSPI) : command is transferred through one I/O pin.

- 1) Address and data are transferred through one pin

- 2) Address is transferred through one pin, data is transferred through two pins

- 3) Address is transferred through one pin, data is transferred through four pins

- 4) Address and data are transferred through two pins

- 5) Address and data are transferred through four pins

- Dual SPI (DSPI) : All command, address and data are transferred through two I/O pins.

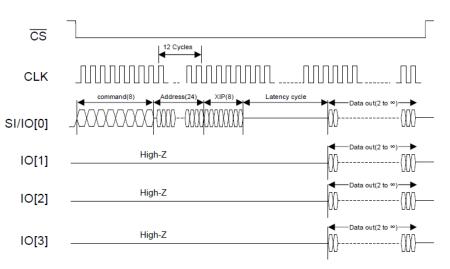

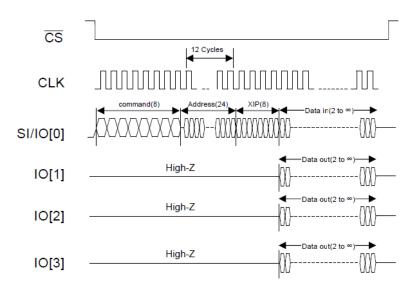

- Quad SPI (QSPI) modes : All command, address and data are transferred through four I/O pins.

- Nomenclature adoption: A typical SPI instruction consists of command, address and data components. The bus width to transmit these three components varies based on the SPI interface mode selected. To accurately represent the number of I/Os used to transmit these three components, a nomenclature (command-address-data) is adopted and used throughout this document. Integers placed in the (command-address-data) fields represent the number of I/Os used to transmit the particular component. As an example, 1-1-1 means command, address and data are transmitted on a single I/O (SI / IO[0] or SO / IO[1]). On the other hand, 1-4-4 represents command being sent on a single I/O (SI / IO[0]) and address/data being sent on four I/Os (IO[3:0]).

CS82xx

| Instruction | Interface Modes (Command-Address-Data) |            |            |            |            |            |            |  |  |  |

|-------------|----------------------------------------|------------|------------|------------|------------|------------|------------|--|--|--|

| Component   | SSPI 1-1-1                             | SSPI 1-1-2 | SSPI 1-2-2 | DSPI 2-2-2 | SSPI 1-1-4 | SSPI 1-4-4 | QSPI 4-4-4 |  |  |  |

| Command     | SI/IO[0]                               | SI/IO[0]   | SI/IO[0]   | IO[1:0]    | SI/IO[0]   | SI/IO[0]   | IO[3:0]    |  |  |  |

| Address     | SI/IO[0]                               | SI/IO[0]   | IO[1:0]    | IO[1:0]    | SI/IO[0]   | IO[3:0]    | IO[3:0]    |  |  |  |

| Data Input  | SI/IO[0]                               | IO[1:0]    | IO[1:0]    | IO[1:0]    | IO[1:0]    | IO[3:0]    | IO[3:0]    |  |  |  |

| Data Output | SO/IO[1]                               | IO[1:0]    | IO[1:0]    | IO[1:0]    | IO[3:0]    | IO[3:0]    | IO[3:0]    |  |  |  |

Table 27 : Pin Assignment / Interface Modes

#### **MSB/LSB** Location in data bits

The most significant bit(MSB) is placed first at all commands, address and data.

## 1Mb ~ 16Mb SPI MRAM

#### Figure 6 : Location of MSB and LSB

For Dual SPI and Quad SPI, the order of data bits is alternately decided among the IO pins.

#### Figure 7 : MSB and LSB in DSPI and QSPI

Note;

All commands, Address, XIP and Data follow this order.

### Data Rate (SDR/DDR)

In Single Data Rate mode (SDR), command, address and data inputs are latched on the rising edge of the clock. Data is outputted on the falling edge of the clock.

#### Figure 8 : Description of SDR Instruction Type

CS82xx

In Double Data Rate mode (DDR), command is latched on the rising edge of the clock. Address and Data inputs are latched on both edges of the clock. Data is output on both edges of the clock.

#### Figure 9 : Description of DDR Instruction Type

#### **Instruction Structure**

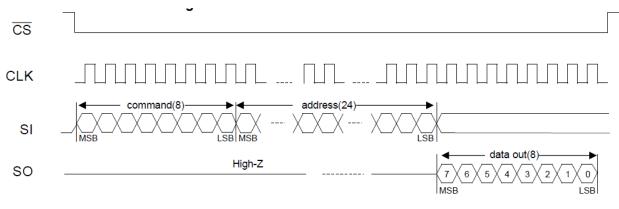

Each instruction starts out with an 8-bit command. The command selects the type of operation. The instruction can be stand alone or followed by address to select a memory location or register. The address is always 24-bits wide.

CS82xx

#### Figure 10 : Description of command followed by Address (SSIP mode)

#### **Read Operation**

Read operation starts from pulling  $\overline{CS}$  Low. 8 bits Read command(03h) is transmitted to the device then 24 bit address is following while the first 7 MSB bits of address are don't care. The device outputs the data at selected address to the SO pin. The read operation can be terminated by pulling  $\overline{CS}$  high.

### Write Operation

Write operation starts from pulling  $\overline{CS}$  Low. 8 bits Write command(02h) is transmitted to the device then 24 bit address is following while the first 7 MSB bits of address are don't care. The data on the SI pin is written to the device at selected address. The write operation can be terminated by pulling  $\overline{CS}$  high.

#### Figure12 : Description of Write Operation (SSPI mode)

CS82xx

Note :

In normal operational mode, write instructions must be preceded by the WREN command. WREN command sets the WREN bit in the Status register. WREN bit is reset at the end of every Write instruction. WREN bit can also be reset by executing the WRDI command. The device offers two other modes, namely SRAM and Back-to-Back Write where WREN does not get reset after a write instruction to the memory array or the augmented 256-byte area. These modes are set in Configuration Register 4.

### **XIP (Execute in Place) Operation**

For read and write operation, the device offers XIP (execute in place) mode. XIP allows a series of read or write operation without loading individual read or write command for each instruction, which results in reduced random-access time. XIP is enabled by entering byte AXh and disabled by entering any byte not equal to AXh. These respective bytes must be entered following the address bits. Read operation with XIP needs extra Read-Latency before data coming out from SO pin. The latencies are specified in Table 19 : Memory Array Read Latency Cycles vs. Maximum Clock Frequency (with XIP).

#### Figure 13 : Description of Read Operation with XIP (SSIP mode)

CS82xx

### **Continuing Read/Write**

The entire memory array can be read from or written to using a single read or write instruction. After the starting address is entered, subsequent address is internally incremented as long as  $\overline{CS}$  is Low and CLK continues toggling.

#### Figure 14 : Description of Continuing Read Operation (SSIP mode)

Next address is automatically incremented

For read operation, the device offers wrap mode. Wrap bursts are confined to address aligned 16/32/64/128/256/512/1K byte boundary. The read address can start anywhere within the wrap boundary. 16/32/64/128/256/512/1K wrap configuration is set in Configuration Register 3.

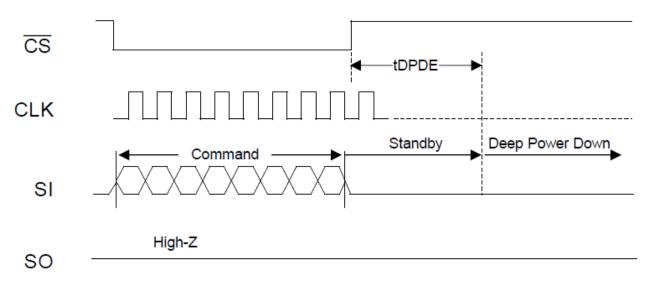

#### **Deep Power Down Modes**

SI

The device provides Deep Power Down mode. This mode reduces current consumption from ISB to IDPD.

To enter the deep power down mode,  $\overline{CS}$  is driven low, following the enter Deep Power Down (DPDE) command,  $\overline{CS}$  must be driven high after the eighth bit of the command code has been latched in or the DPDE command will not be executed. After  $\overline{CS}$  is driven high, it requires a delay of tDPDE before the supply current is reduced to IDPD and the Deep Power Down mode is entered. The command can be issued in SPI, DSPI or QSPI modes.

## 1Mb ~ 16Mb SPI MRAM

#### Figure 16 : Entering Deep Power Down Mode (SSIP mode)

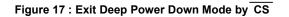

• There are two ways to exit deep power down mode:

- 1. Toggling CS with a CS pulse width of tCSDPD while CLK and I/Os are Don't Care. During waking up from deep power down, I/Os remain to be in high-Z.

- 31

2. Driving CS low follows with the Exit Deep Power Down (EXDPD, ABh) command. CS must be driven high after the eight bits of the command code has been latched in or the EXDPD command will not be executed.

### 1Mb ~ 16Mb SPI MRAM

#### Figure 18 : Exit Deep Power Down Mode by SPI Command

- It requires a delay of tEXDPD before the device can fully exit the deep power down mode and enter standby mode.

- Status of all non-volatile bits in registers remains unchanged when the device enters or exits the deep power down mode.

- The command can be issued in SPI, DPI, and QPI mode.

#### **Software Reset**

Software Reset (SRST) requires Software Reset Enable (SRTE) implemented in advance.

#### Figure 19 : Software Reset Timing

## 1Mb ~ 16Mb SPI MRAM

#### **JEDEC Reset**

#### Figure 20 : JEDEC Reset Operation Timing

#### Table 28 : JEDEC Reset Operation & Timing : 1.8V Device

| Parameter                | Symbol             | Min. | Max. | Units |

|--------------------------|--------------------|------|------|-------|

| CS Low Time              | t <sub>CSL</sub>   | 0.5  | -    | μs    |

| CS High Time             | t <sub>CSH</sub>   | 0.5  | -    | μs    |

| SI Setup Time (w.r.t CS) | t <sub>SU</sub>    | 5.0  | -    | ns    |

| SI Hold Time (w.r.t CS)  | t <sub>HD</sub>    | 5.0  | -    | ns    |

| JEDEC Hardware Reset     | t <sub>RESET</sub> | -    | 2.0  | ms    |

#### Table29 : JEDEC Reset Operation & Timing : 3.3V Device

| Parameter                | Symbol             | Min. | Max. | Units |

|--------------------------|--------------------|------|------|-------|