# **Revision History**

## Rev. No.

## <u>History</u>

1.0

New issue

## **Issue Date**

Aug. 07,2023

# High Power GaN FET Half-Bridge Power Stage

### Description

The CS9200 device is an 80V GaN power stage, driving current up to 10A, provides an integrated solution using enhancement-mode Gallium Nitride (GaN) FETs. The device consists of two 80V GaN FETs driven by one high-frequency GaN FET driver in a half-bridge configuration. All the devices are mounted on a completely bond-wire free package platform with minimized package parasitic elements.

The device extends advantages of discrete GaN FETs by offering a more user-friendly interface. It is an ideal solution for applications requiring high frequency, high-efficiency operation in a small form factor.

The CS9200 device is available in a  $6 \times 8 \times 1.39$  mm 9L LGA lead-free package and can be easily mounted on PCBs.

### Features

- Independent High-Side and Low-Side CMOS Logic Inputs

- Integrated 3.7mΩ GaN FETs and Driver

- High-Side input Voltage Rail Operates up to 80V

- Fast Propagation Times (30ns Typical)

- Excellent Propagation Delay Matching (2ns Typical)

- Supply Rail Under-Voltage Lockout

- Package Optimized for Easy PCB Layout, Eliminating Need for Underfill, Creepage, and Clearance Requirements

# Applications

- Class D Amplifiers for Audio

- Current Fed Push-Pull converters

- Synchronous Buck converters

- Two-switch Forward converters

- High Power Density Single- and Three-Phase Motor Drive

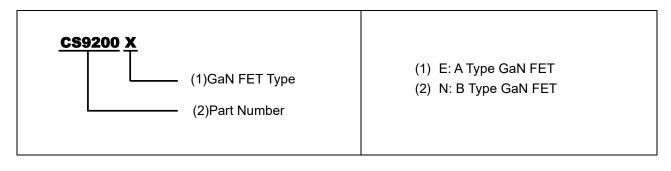

## Ordering & Marking Information

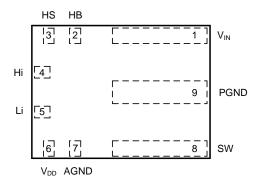

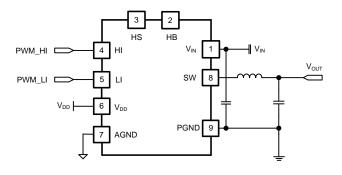

# Pin Configuration

## Pin Description

| PIN NO. | SYMBOL          | DESCRIPTION                                     |  |  |  |

|---------|-----------------|-------------------------------------------------|--|--|--|

| 1       | VIN             | Input voltage pin.                              |  |  |  |

| 2       | HB              | High-Side Bootstrap                             |  |  |  |

| 3       | HS              | High-side source connection.                    |  |  |  |

| 4       | Н               | High–Side Input                                 |  |  |  |

| 5       | LI              | Low-Side Input                                  |  |  |  |

| 6       | V <sub>DD</sub> | 5-V positive gate drive supply.                 |  |  |  |

| 7       | AGND            | Analog ground.                                  |  |  |  |

| 8       | SW              | Switching node. Electrically shorted to HS pin. |  |  |  |

| 9       | PGND            | Power ground. Low-side GaN FET source.          |  |  |  |

Rev. 1.0

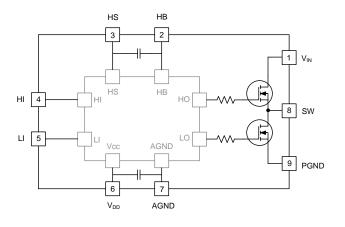

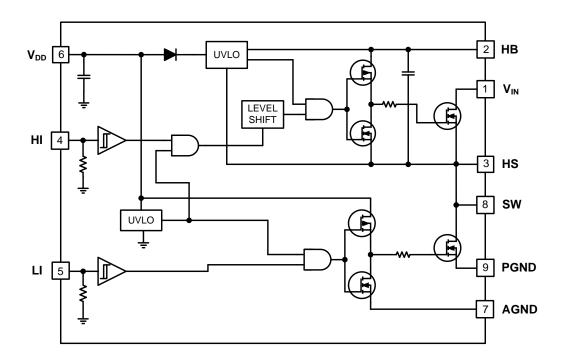

### Simplified Block Diagram

#### Absolute Maximum Ratings (Note 1)

| PARAMETER                 | RATINGS    | UNIT |

|---------------------------|------------|------|

| V <sub>IN</sub> to PGND   | 0~+80      | V    |

| HB to AGND                | -0.3 ~ +87 | V    |

| HS to AGND                | -5~+80     | V    |

| V <sub>DD</sub> to AGND   | -0.3 ~ +7  | V    |

| HB to HS                  | -0.3 ~ +7  | V    |

| HB to VDD                 | 0~+80      | V    |

| SW to PGND                | -5 ~ +80   | V    |

| LI or HI Input            | -0.3 ~ +7  | V    |

| Junction Temperature      | 125        | °C   |

| Storage Temperature Range | -40~+150   | °C   |

#### Recommended Operation Conditions (Note 2)

| PARAMETER            | RATINGS                                   | UNIT |

|----------------------|-------------------------------------------|------|

| VIN                  | 0~+80                                     |      |

| V <sub>DD</sub>      | +4.5~+5.5                                 | V    |

| LI or HI Input       | 0~+5.5                                    | V    |

| HS                   | -5~80                                     | V    |

| НВ                   | V <sub>HS</sub> +4 ~ V <sub>HS</sub> +5.5 | V    |

| HS Slew Rate         | <50                                       | V/ns |

| Junction Temperature | -40~+125                                  | °C   |

Note 1: Stresses listed as the above "Absolute Maximum Ratings" may cause permanent damage to the device.

These are for stress ratings. Functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may remain possibility to affect device reliability.

Note 2: Design properly at all application environment, the device is not guaranteed to function outside its operating conditions.

## **Electrical Characteristics**

Typical values represent the most likely parametric norm at  $T_A=25$  °C, and are provided for reference purposes only. Unless otherwise specified,  $V_{DD}=V_{HB}=5V$ .

| PARAMETER                                                                          | SYMBOL                | CONDITIONS                                                                                        | MIN  | ТҮР  | MAX  | UNIT |

|------------------------------------------------------------------------------------|-----------------------|---------------------------------------------------------------------------------------------------|------|------|------|------|

| SUPPLY CURRENTS                                                                    |                       |                                                                                                   |      |      |      |      |

| V <sub>DD</sub> Quiescent Current                                                  | IDD                   | LI=HI=0V, V <sub>DD</sub> =V <sub>HB</sub> =5V                                                    |      | 0.08 |      | mA   |

| VDD Operating Current                                                              | Iddo                  | f=500kHz                                                                                          |      | 4.5  |      | mA   |

| Total HB Quiescent Current                                                         | Інв                   | LI=HI=0V                                                                                          |      | 0.09 |      | mA   |

| Total HB Operating Current                                                         | Інво                  | f=500kHz                                                                                          |      | 4.5  |      | mA   |

| INPUT                                                                              |                       |                                                                                                   |      |      |      |      |

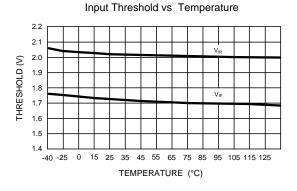

| Input Voltage Threshold                                                            | VIR                   | Rising Edge                                                                                       | 1.85 | 2    | 2.15 | V    |

| Input Voltage Threshold                                                            | VIF                   | Falling Edge                                                                                      | 1.55 | 1.7  | 1.85 | V    |

| Input Voltage Hysteresis                                                           | VIHYS                 |                                                                                                   |      | 300  |      | mV   |

| Input Pulldown Resistance                                                          | Rı                    |                                                                                                   |      | 200  |      | kΩ   |

| UNDER VOLTAGE PROTECTION                                                           | N                     |                                                                                                   |      |      |      |      |

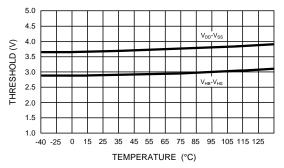

| V <sub>DD</sub> rising threshold                                                   | V <sub>DDR</sub>      |                                                                                                   | 3.2  | 3.8  | 4.5  | V    |

| V <sub>DD</sub> threshold hysteresis                                               | Vddh                  |                                                                                                   |      | 0.25 |      | V    |

| HB rising threshold                                                                | Vhbr                  |                                                                                                   | 2.4  | 3.1  | 3.8  | V    |

| HB threshold hysteresis                                                            | Vнвн                  |                                                                                                   |      | 0.25 |      | V    |

| POWER STAGE                                                                        |                       |                                                                                                   |      |      |      |      |

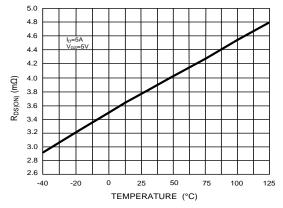

| High-side GaN FET on-resistance                                                    | Rds(on)hs             | LI=0V, HI=V <sub>DD</sub> =5V, HB-HS=5V, V <sub>IN</sub> -SW=5A, T <sub>J</sub> = 25 $^{\circ}$ C |      | 3.7  | 4.5  | mΩ   |

| Low-side GaN FET on-resistance                                                     | Rds(on)ls             | LI=V <sub>DD</sub> =5V, HI=0V, HB-HS=5V,<br>SW-PGND=5A, TJ = 25℃                                  |      | 3.7  | 4.5  | mΩ   |

| SW to $V_{IN}$ Forward Voltage                                                     | V <sub>SD</sub>       | $I_{SD}$ =500mA, V <sub>IN</sub> floating, V <sub>DD</sub> =5V, HI=LI=0V                          |      | 1.5  |      | V    |

| Leakage from V <sub>IN</sub> to SW, the high-<br>side and low-side GaN FET are off | I <sub>L-VIN-SW</sub> | V <sub>IN</sub> =80V, HI=LI=0V, V <sub>DD</sub> =5V,<br>TJ=25℃                                    |      | 80   | 350  | μA   |

| Leakage from SW to GND, the high-<br>side and low-side GaN FET are off             | IL-SW-GND             | SW=80V, HI=LI=0V, V <sub>DD</sub> =5V,<br>T <sub>J</sub> =25°C                                    |      | 80   | 350  | μA   |

# **Electrical Characteristics (continued)**

Typical values represent the most likely parametric norm at  $T_A=25$  °C, and are provided for reference purposes only. Unless otherwise specified,  $V_{DD}=V_{HB}=5V$ .

| PARAMETER                      | SYMBOL | CONDITIONS    | MIN | ТҮР  | MAX | UNIT |

|--------------------------------|--------|---------------|-----|------|-----|------|

| BOOTSTRAP DIODE AND CLAMP      |        |               |     |      |     |      |

| Low Current forward voltage    | Vdl    | Ivdd-нв=100µА |     | 0.4  |     | V    |

| High Current forward voltage   | Vdh    | Ivdd-нв=50mA  |     | 0.9  |     | V    |

| Dynamic resistance             | R⊳     | Ivdd-нв=50mA  |     | 1.85 | 3.6 | Ω    |

| HB-HS clamp regulation voltage | VCLAMP |               | 4.5 | 5    | 5.5 | V    |

#### Switching Characteristics(over operating free-air temperature range)

| PARAMETER                                         | SYMBOL             | CONDITIONS                                                    | MIN | ТҮР | MAX | UNIT |

|---------------------------------------------------|--------------------|---------------------------------------------------------------|-----|-----|-----|------|

| Propagation delay: HI Rising                      | t <sub>HIPLH</sub> | LI=0V, V <sub>DD</sub> =5V, HB-HS=5V,<br>V <sub>IN</sub> =30V |     | 30  | 60  | ns   |

| Propagation delay: HI Falling                     | thiphl             | LI=0V, V <sub>DD</sub> =5V, HB-HS=5V,<br>V <sub>IN</sub> =30V |     | 30  | 60  | ns   |

| Propagation delay: LI Rising                      | tlplh              | HI=0V, V <sub>DD</sub> =5V, HB-HS=5V,<br>V <sub>IN</sub> =30V |     | 30  | 60  | ns   |

| Propagation delay: LI Falling                     | <b>t</b> LPHL      | HI=0V, V <sub>DD</sub> =5V, HB-HS=5V,<br>V <sub>IN</sub> =30V |     | 30  | 60  | ns   |

| Delay matching: LI high & HI low                  | t <sub>MON</sub>   |                                                               |     | 2   | 8   | ns   |

| Delay matching: LI low & HI high                  | <b>t</b> MOFF      |                                                               |     | 2   | 8   | ns   |

| Minimum input pulse width that changes the output | t <sub>PW</sub>    |                                                               |     | 10  |     | ns   |

# **Typical Application Circuit**

# Functional Block Diagram

#### Detailed Operating Description

The CS9200 is half-bridge, GaN power stage with highly integrated high-side and low-side gate drivers, which includes built-in UVLO protection circuitry and an overvoltage clamp circuitry. The device integrates two, 3.7mΩ GaN FETs in a half-bridge configuration. The device can be used in many isolated and non-isolated topologies allowing very simple integration. The LGA package is designed to minimize the loop inductance while keeping the PCB design simple.

The built-in bootstrap circuit with clamp prevents the high-side gate drive from exceeding the GaN FETs maximum gateto-source voltage without any additional external circuitry. The built-in driver has an undervoltage lockout (UVLO) on the V<sub>DD</sub> and bootstrap (HB-HS) rails. When the voltage is below the UVLO threshold voltage, the device ignores both the HI and LI signals to prevent the GaN FETs from being partially turned on.

#### PWM Inputs

The CS9200's inputs pins are independently controlled. This inputs to be directly connected to the outputs of an analog PWM controller with to 5V power supply. Allow flexibility to optimize deadtime according to design needs, the CS9200 does not implement an overlap protection functionality. If both HI and LI are asserted, both the high-side and low-side GaN FETs are turned on. Careful consideration must be applied to the control inputs in order to avoid a shoot-through condition.

#### High-Side Driver

The high-side driver is designed to "float" meaning that its reference (ground) floats with the SW pin of the CS9200 which is normally tied to the source of an N channel GaN FET. The bias voltage to the high-side driver is supplied to the HB pin through a bootstrap switch (diode), so that a internal capacitor(HB-HS), can be charged up each time the low side GaN device is turned on. As the high-side GaN FET turns on, SW rises to VIN, forcing the HB pin voltage to VIN+VDD that provides a voltage to hold the high-side GaN FET on.

The high-side bias voltage is generated using a bootstrap technique and is internally clamped at 5V(typ). This clamp prevents the gate voltage from exceeding the maximum gate-source voltage rating of the enhancement-mode GaN FETs.

### Low-Side Driver

The low-side driver is designed to drive a ground referenced GaN FET. The bias to the low-side driver is internally connected to V<sub>DD</sub> supply and GND.

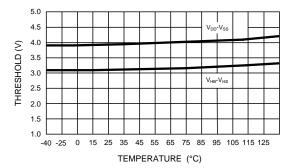

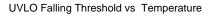

#### Start-up and UVLO

The CS9200 has an Under-voltage Lockout (UVLO) on both the V<sub>DD</sub> and bootstrap supplies. When the V<sub>DD</sub> voltage is below the threshold voltage of 3.8V, both the HI and LI inputs are ignored, to prevent the FETs from being partially turned on. Also if there is sufficient V<sub>DD</sub> voltage, the driver actively pulls the high-side and low-side gate driver output low. The UVLO threshold hysteresis of 200 mV prevents chattering and unwanted turnon due to voltage spikes.

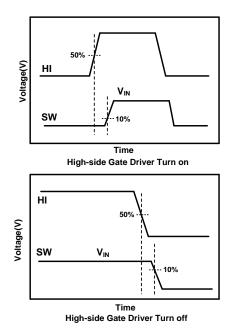

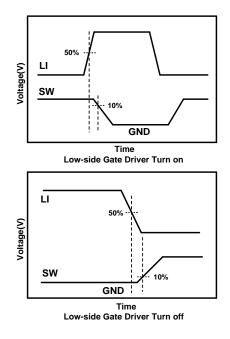

#### Propagation Delay Measurement

Below figure shows the definitions of the turn-on and turn-off propagation delay times.

## Typical Characteristics

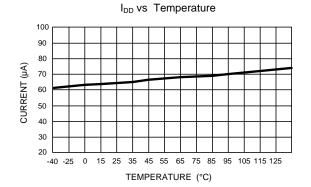

UVLO Rising Threshold vs Temperature

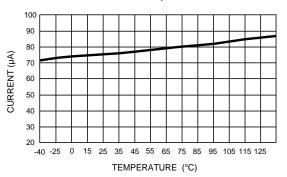

I<sub>HB</sub> vs Temperature

g Rev. 1.0 Chiplus reserves the right to change product or specification without notice.

**Typical Characteristics** (continued)

Input Threshold Hysteresis vs Temperature

GaN FET on-resistance vs Temperature

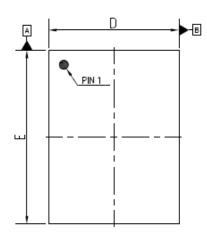

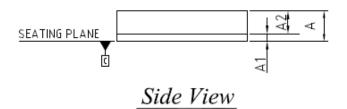

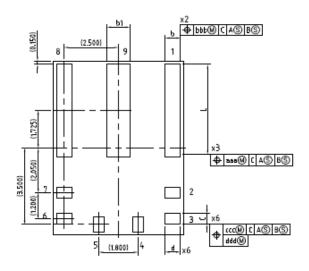

# Package Dimension

9L LGA package outline 6 x 8 x 1.39 mm body size

Top View

# Bottom View

| Symbol | Dimension in mm |      |       |  |  |  |  |

|--------|-----------------|------|-------|--|--|--|--|

| Symbol | Min             | Norm | Max   |  |  |  |  |

| Α      | 1.33            | 1.39 | 1.4.4 |  |  |  |  |

| A1     | 0.30            | 0.34 | 0.38  |  |  |  |  |

| A2     | 1.03            | 1.05 | 1.06  |  |  |  |  |

| D      | 5.90            | 6.00 | 6.10  |  |  |  |  |

| E      | 7.90            | 8.00 | 8.10  |  |  |  |  |

| b      | 0.65            | 0.70 | 0.75  |  |  |  |  |

| b1     | 1.00            | 1.05 | 1.10  |  |  |  |  |

| L      | 4.20            | 4.25 | 4.30  |  |  |  |  |

| с      | 0.45            | 0.50 | 0.55  |  |  |  |  |

| d      | 0.65            | 0.70 | 0.75  |  |  |  |  |

| 999    | 0.05            |      |       |  |  |  |  |

| bbb    | 0.05            |      |       |  |  |  |  |

| CCC    | 0.10            |      |       |  |  |  |  |

| ddd    | 0.08            |      |       |  |  |  |  |