# **Revision History**

## Rev. No.

<u>History</u>

1.0

New issue

#### **Issue Date**

Oct. 05,2022

# **Dual-Channel Gate Driver for Enhancement Mode GaN FETs**

### Description

The CS8201 is a high performance dual gate driver optimized to drive half bridge N-Channel GaN FETs. A high floating top driver design can accommodate HB voltage as high as 80V. The CS8201 has split gate outputs, providing flexibility to adjust the turn-on and turn-off strength independently.

In addition, the strong sink capability of the CS8201 maintains the gate in the low state, preventing unintended turn-on during switching. The CS8201 can operate up to several MHz. This device also supports supply input under voltage lockout.

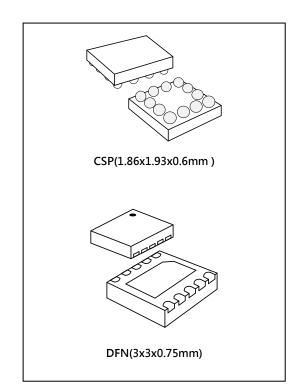

The CS8201 uses 12 balls CSP package. and 10L DFN- 3x3x0.75mm.

#### Features

- Independent High-Side and Low-Side TTL Logic Inputs

- 1.2A/5A Peak Source/Sink Current

- High-Side Floating Bias Voltage Rail Operates up to 80V<sub>DC</sub>

- Split Outputs for Adjustable Turn-on/Turn-off Strength

- $0.6\Omega / 2.1\Omega$  Pull-down/Pull-up Resistance

- Fast Propagation Times (30ns Typical)

- Excellent Propagation Delay Matching (1.5ns Typical)

- Supply Rail Under-Voltage Lockout

- Low Power Consumption

#### Applications

- Current Fed Push-Pull converters

- Half and Full-Bridge converters

- Synchronous Buck converters

- Two-switch Forward converters

- Forward with Active Clamp converters

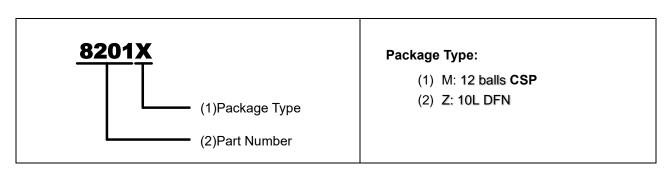

# Ordering & Marking Information

2

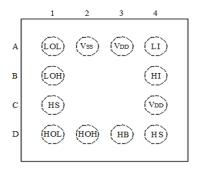

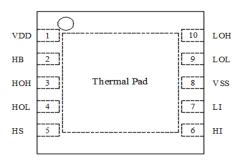

Pin Configuration

# **CS8201**

12 balls CSP (Top View)

10L DFN (Top View)

#### Pin Description

| PIN NO. | SYMBOL          | DESCRIPTION                                                                           |

|---------|-----------------|---------------------------------------------------------------------------------------|

| A3,C4   | V <sub>DD</sub> | Power Supply Pin                                                                      |

| D3      | HB              | High-Side Bootstrap                                                                   |

| D2      | НОН             | High-side gate driver turn-on output, use a resistor to set the turn-on speed.        |

| D1      | HOL             | High-side gate driver tum-off output, use a resistor to set the turn-off speed.       |

| C1,D4   | HS              | High-side source connection                                                           |

| B4      | HI              | High–Side Input                                                                       |

| A4      | LI              | Low-Side Input                                                                        |

| A2      | Vss             | Ground                                                                                |

| A1      | LOL             | Low-side gate driver sink-current output, use a resistor to set the turn-off speed.   |

| B1      | LOH             | Low-side gate driver source- current output, use a resistor to set the turn-on speed. |

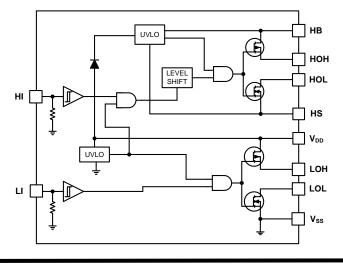

## Functional Block Diagram

3

#### Absolute Maximum Ratings (Note 1)

| PARAMETER                          | RATINGS                                     | UNIT |

|------------------------------------|---------------------------------------------|------|

| V <sub>DD</sub> to V <sub>SS</sub> | -0.3 ~ 7                                    | V    |

| HB to HS                           | -0.3 ~ 7                                    | V    |

| LI or HI Input                     | -0.3 ~ 7                                    | V    |

| LOH, LOL Output                    | -0.3 ~ V <sub>DD</sub> +0.3                 | V    |

| HOH, HOL Output                    | V <sub>HS</sub> -0.3 ~ V <sub>HB</sub> +0.3 | V    |

| HS to Vss                          | −5V ~ +80                                   | V    |

| HB to Vss                          | 0~87                                        | V    |

| HB to VDD                          | 0~80                                        | V    |

| Junction Temperature               | 150                                         | °C   |

| Storage Temperature Range          | -55 ~ +150                                  | °C   |

#### Recommended Operation Conditions (Note 2)

| PARAMETER            | RATINGS                                   | UNIT |

|----------------------|-------------------------------------------|------|

| VDD                  | +4.5 ~ +5.5                               | V    |

| Ll or Hl Input       | 0~+5.5                                    | V    |

| HS                   | -5~80                                     | V    |

| НВ                   | V <sub>HS</sub> +4 ~ V <sub>HS</sub> +5.5 | V    |

| HS Slew Rate         | <50                                       | V/ns |

| Junction Temperature | -40~+125                                  | °C   |

Note 1:Stresses listed as the above "Absolute Maximum Ratings" may cause permanent damage to the device.

These are for stress ratings. Functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may remain possibility to affect device reliability.

Note 2:The device is not guaranteed to function outside its operating conditions.

# **CS8201**

#### Electrical Characteristics

Typical values represent the most likely parametric norm at  $T_A=25$  °C, and are provided for reference purposes only. Unless otherwise specified,  $V_{DD}=V_{HB}=5V$ ,  $V_{SS}=V_{HS}=0V$ , No Load on LOL and HOL or HOH and HOL.

| PARAMETER                                                        | SYMBOL            | L CONDITIONS                                   |      | ТҮР  | МАХ  | UNIT |  |

|------------------------------------------------------------------|-------------------|------------------------------------------------|------|------|------|------|--|

| SUPPLY CURRENTS                                                  |                   |                                                |      |      |      |      |  |

| V <sub>DD</sub> Quiescent Current                                | IDD               | LI=HI=0V, V <sub>DD</sub> =V <sub>HB</sub> =4V |      | 0.08 |      | mA   |  |

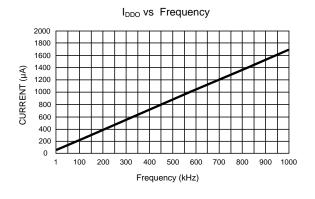

| V <sub>DD</sub> Operating Current                                | Iddo              | f=500kHz                                       |      | 1.8  |      | mA   |  |

| Total HB Quiescent Current                                       | Інв               | LI=HI=0V                                       |      | 0.09 |      | mA   |  |

| Total HB Operating Current                                       | Інво              | f=500kHz                                       |      | 1.4  |      | mA   |  |

| HB to Vss Current, Quiescent                                     | I <sub>HBS</sub>  | HS=HB=80V                                      |      | 0.4  |      | μA   |  |

| HB to Vss Current, Operating                                     | I <sub>HBSO</sub> | f=500kHz                                       |      | 0.35 |      | mA   |  |

| INPUT                                                            |                   |                                                |      | •    |      |      |  |

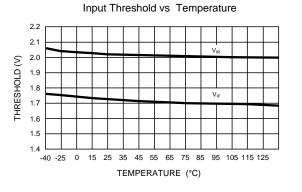

| Input Voltage Threshold                                          | VIR               | Rising Edge                                    | 1.85 | 2    | 2.15 | V    |  |

| Input Voltage Threshold                                          | VIF               | Falling Edge                                   | 1.55 | 1.7  | 1.85 | V    |  |

| Input Voltage Hysteresis                                         | VIHYS             |                                                |      | 300  |      | mV   |  |

| Input Pulldown Resistance                                        | Rı                |                                                |      | 200  |      | kΩ   |  |

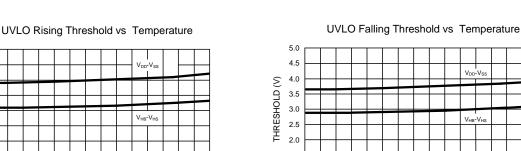

| UNDER VOLTAGE PROTECTI                                           | ON                |                                                | •    | •    |      |      |  |

| $V_{DD}$ rising threshold                                        | Vddr              |                                                | 3.2  | 3.8  | 4.5  | V    |  |

| V <sub>DD</sub> threshold hysteresis                             | Vddh              |                                                |      | 0.25 |      | V    |  |

| HB rising threshold                                              | VHBR              |                                                | 2.4  | 3.1  | 3.8  | V    |  |

| HB threshold hysteresis                                          | Vнвн              |                                                |      | 0.25 |      | V    |  |

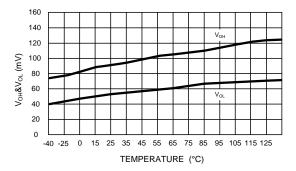

| LOW & HIGH SIDE GATE DRIV                                        | /ER               |                                                |      | •    |      |      |  |

| Low-level output voltage                                         | Vol               | I <sub>HOL</sub> =I <sub>LOL</sub> =100 mA     |      | 0.06 |      | V    |  |

| High-level output voltage                                        |                   |                                                |      |      |      |      |  |

| V <sub>OH</sub> =V <sub>DD</sub> -LOH or V <sub>OH</sub> =HB-HOH | Vон               | I <sub>НОН</sub> =I <sub>∟ОН</sub> =100 mA     |      | 0.2  |      | V    |  |

| Peak source current                                              | IOHL              | HOH,LOH=0 V                                    |      | 1.2  |      | А    |  |

| Peak sink current                                                | Ioll              | HOL,LOL=5 V                                    |      | 5    |      | А    |  |

| High-level output leakage current                                | Іонік             | HOH,LOH=0 V                                    |      | 0.2  | 1.0  | μA   |  |

| Low-level output leakage current                                 | Iollk             | HOL,LOL=5 V                                    |      | 0.2  | 1.0  | μA   |  |

## **Electrical Characteristics (continued)**

Typical values represent the most likely parametric norm at TA=25°C, and are provided for reference purposes only. Unless otherwise specified,  $V_{DD}=V_{HB}=5V$ ,  $V_{SS}=V_{HS}=0V$ , No Load on LOL and HOL or HOH and HOL.

| PARAMETER                      | SYMBOL          | CONDITIONS                 | MIN | ТҮР  | МАХ | UNIT |

|--------------------------------|-----------------|----------------------------|-----|------|-----|------|

| BOOTSTRAP DIODE AND CLAMP      |                 |                            |     |      |     |      |

| Low Current forward voltage    | V <sub>DL</sub> | I <sub>∨DD-нв</sub> =100µА |     | 0.4  |     | V    |

| High Current forward voltage   | VDH             | I <sub>VDD-HB</sub> =50mA  |     | 0.9  |     | V    |

| Dynamic resistance             | RD              | I <sub>VDD-HB</sub> =50mA  |     | 1.85 | 3.6 | Ω    |

| HB-HS clamp regulation voltage | VCLAMP          |                            | 4.5 | 5    | 5.5 | V    |

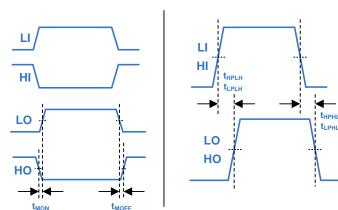

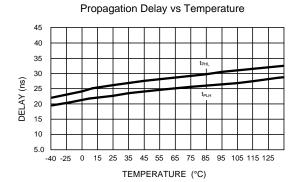

#### **Switching Characteristics**(over operating free-air temperature range)

| PARAMETER                                         | SYMBOL            | CONDITIONS                | MIN | ТҮР | МАХ | UNIT |

|---------------------------------------------------|-------------------|---------------------------|-----|-----|-----|------|

| LO turn-off propagation delay                     | tlphl             | LI falling to LOL falling |     | 30  | 45  | ns   |

| LO turn-on propagation delay                      | t <sub>LPLH</sub> | LI rising to LOH rising   |     | 30  | 45  | ns   |

| HO turn-off propagation delay                     | thphl             | HI falling to HOL falling |     | 30  | 45  | ns   |

| HO turn-on propagation delay                      | t <sub>HPLH</sub> | HI rising to HOH rising   |     | 30  | 45  | ns   |

| Delay matching<br>LO on & HO off                  | t <sub>MON</sub>  |                           |     | 1.5 | 8   | ns   |

| Delay matching<br>LO off & HO on                  | t <sub>MOFF</sub> |                           |     | 1.5 | 8   | ns   |

| HO rise time (0.5 V~4.5 V)                        | t <sub>HRC</sub>  | C <sub>L</sub> =1000 pF   |     | 7   |     | ns   |

| LO rise time (0.5 V~4.5 V)                        | t <sub>LRC</sub>  | C∟=1000 pF                |     | 7   |     | ns   |

| HO fall time (0.5 V~4.5 V)                        | tнғс              | C∟=1000 pF                |     | 4   |     | ns   |

| LO fall time (0.5 V~4.5 V)                        | tlfc              | C∟=1000 pF                |     | 4   |     | ns   |

| Minimum input pulse width that changes the output | tPW               |                           |     | 10  |     | ns   |

#### Detailed Operating Description

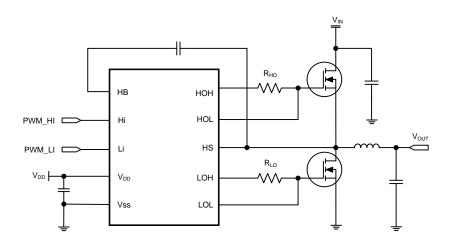

The CS8201 is designed to drive both the high-side and the low-side enhancement mode FETs in a synchronous buck or a half-bridge configuration. The CS8201 input has two separate HI and LI, the signaleach driving high side and Low side GaN FETs. HI logic high turns on the high-side gate driver and turns off the lowside gate driver. In reverse,LI logic high turns off the high side gate driver and turns on the low side gate driver. If not used, it must be tied to the GND. These inputs must not be kept floating.

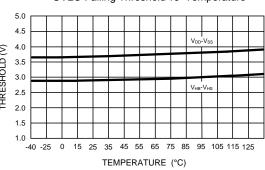

The CS8201 has an Under-voltage Lockout (UVLO) on both the V<sub>DD</sub> and bootstrap supplies. When the V<sub>DD</sub> voltage is below the threshold voltage of 3.8V, both the HI and LI inputs are ignored, to prevent the FETs from being partially turned on. Also if there is sufficient V<sub>DD</sub> voltage, the UVLO will actively pull the LOL and HOL low. When the HB to HS bootstrap voltage is below the UVLO threshold of 3.1V, only HOL is pulled low.

#### High-Side Driver

The high side driver uses the floating bootstrap capacitor voltage to drive the high-side FETs The bootstrap capacitor is recharged through an internal bootstrap diode each cycle when the HS pin is pulled below the  $V_{DD}$  voltage. For inductive load applications the HS node will fall to a negative potential, clamped by the low side FETs. Between HOH and HOL Pin, use a resistor(R<sub>HO</sub>) to set the turn-on speed, the recommended resistance value is above 30 $\Omega$ .

#### Low-Side Driver

The low-side driver is designed to drive a ground referenced FETs, The bias to the low-side driver s internally connected to  $V_{DD}$  supply and GND. Between LOH and LOL Pin, use a resistor(R<sub>LO</sub>) to set the turn-on speed, the recommended resistance value is above 10 $\Omega$ .

#### Timing Diagram

#### Truth Table

| н | U | НОН  | HOL  | LOH  | LOL  |

|---|---|------|------|------|------|

| L | L | Open | L    | Open | L    |

| L | Н | Open | L    | Н    | Open |

| н | L | Н    | Open | Open | L    |

| н | Н | Н    | Open | Н    | Open |

I<sub>HBO</sub> vs Frequency CURRENT (µA) Frequency (kHz)

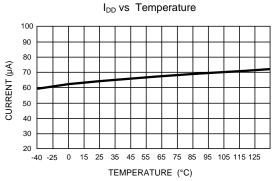

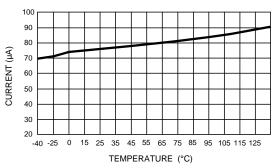

I<sub>HB</sub> vs Temperature

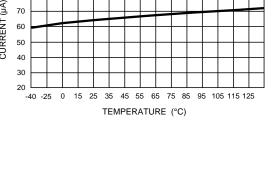

I<sub>HB</sub> vs Temperature

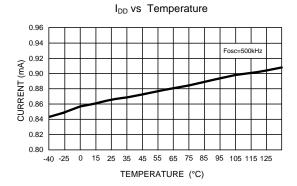

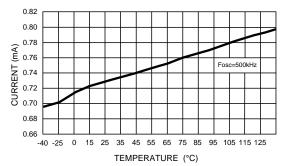

**Typical Characteristics** (continued)

# **CS8201**

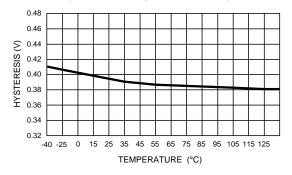

Input Threshold Hysteresis vs Temperature

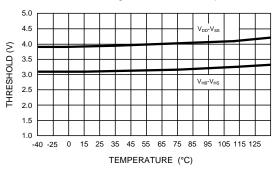

HO & LO Gate Drive vs Temperature

Rev. 1.0 9 Chiplus reserves the right to change product or specification without notice.

#### Typical Applications

### Layout Guidelines

Gate drivers experience high di/dt during the switching transitions. So, the inductance at the gate drive traces must be minimized to avoid excessive ringing on the switch node. Gate drive traces should be kept as short and wide as practical. The input capacitor must be placed as close as possible to the IC. Connect the  $V_{SS}$  pin of the CS8201 as close as possible to the source of the lower FETs. The use of vias is highly desirable to maximize thermal conduction away from driver.

**CS8201**

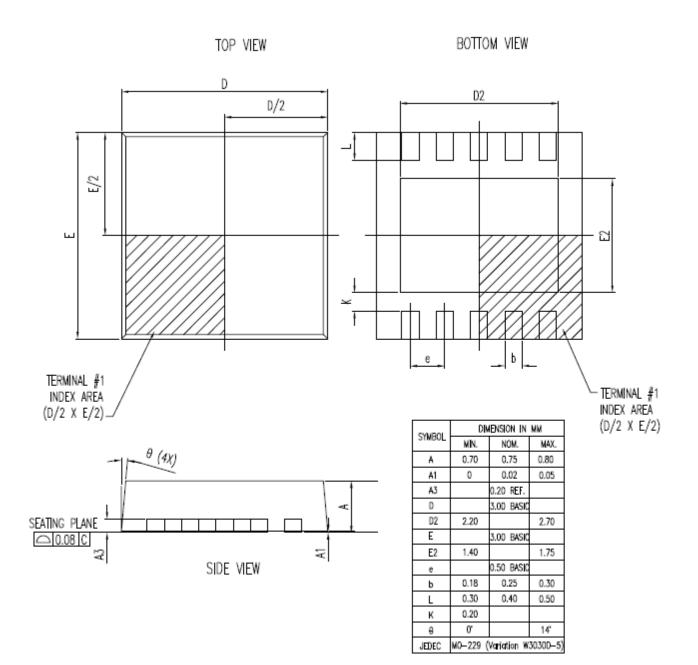

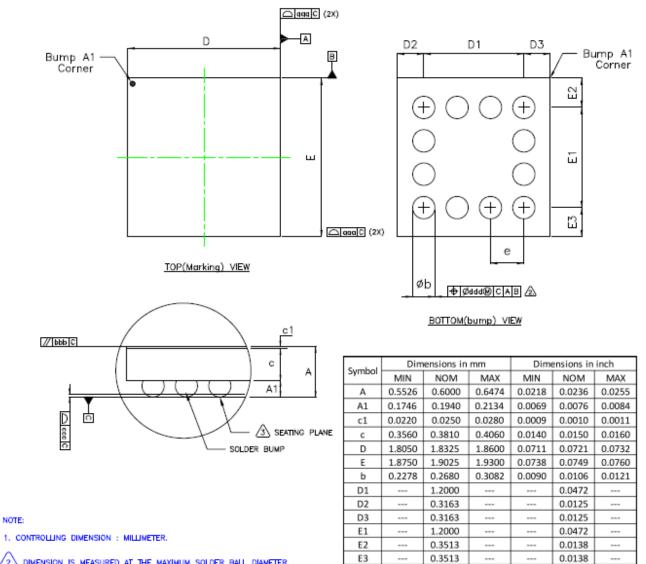

#### Package outline

12 balls CSP with 1.86x1.93mm body size

2. DIMENSION IS MEASURED AT THE MAXIMUM SOLDER BALL DIAMETER, PARALLEL TO PRIMARY DATUM C

3. PRIMARY DATUM C AND SEATING PLANE ARE DEFINED BY THE SPHERICAL CROWNS OF THE SOLDER BALLS

e

aaa

bbb

CCC

ddd

---

0.4000

0.0275

0.0600

0.0300

0.0150

----

----

----

0.0157

0.0011

0.0024

0.0012

0.0006

----

----

----

10 L DFN-3x3x0.75mm